madnan479

Newbie level 3

Hi,

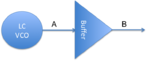

This is second post on this forum. I am trying to understand contribution of buffer in the phase noise of LC VCO in any CMOS process especially at the low offset frequencies (1/f³ region).

When one adds a buffer with the VCO core and simulate phase noise at both VCO output and the buffer output, the phase noise at the far offsets starts degrading at the buffer output compared with VCO output. The only way to recover the performance is to burn more current in the buffer.

Things become more interesting when we look at the behavior in the 1/f³ region. First of all, in the deep scaled CMOS processes, the buffer seems to contribute considerable amount of phase noise at low offset frequencies. Confusing part is even if the phase noise is probed at the output of VCO (and not at the buffer output) the buffer contribution is present there (from the noise contribution summary table). Assumption is, there is no feedback path between the output and the input of buffer. How does the flicker noise of buffer upconvert to carrier and appear at the VCO as well as buffer output? Any insight?

This is second post on this forum. I am trying to understand contribution of buffer in the phase noise of LC VCO in any CMOS process especially at the low offset frequencies (1/f³ region).

When one adds a buffer with the VCO core and simulate phase noise at both VCO output and the buffer output, the phase noise at the far offsets starts degrading at the buffer output compared with VCO output. The only way to recover the performance is to burn more current in the buffer.

Things become more interesting when we look at the behavior in the 1/f³ region. First of all, in the deep scaled CMOS processes, the buffer seems to contribute considerable amount of phase noise at low offset frequencies. Confusing part is even if the phase noise is probed at the output of VCO (and not at the buffer output) the buffer contribution is present there (from the noise contribution summary table). Assumption is, there is no feedback path between the output and the input of buffer. How does the flicker noise of buffer upconvert to carrier and appear at the VCO as well as buffer output? Any insight?

Last edited: