shainky

Junior Member level 1

Hi All,

I am facing difficulty in understanding certain concepts.

Could you please clarify my following doubts:

1) Is there any example of having an intentional combo loop in design? Can combo loops be useful? How does synthesis tool and gate level simulation act on combo loop. How do we meet timings of combo loops?

2) How do we meet timings of mux? Do we need to do setcase analysis at all select inputs of mux or does synthesis tool do it for us?

3) Can we have useful latches in our design? Can we use it at any other place than during DFT?

4) The latch borrowing concept...i see it written that it is for fixing hold problems. Latch borrowing is done to increase the sampling time to half clock period, then how does it fix the hold issue? Doesnt it mean increasing the time for setup?

The latch borrowing concept that i have seen is wrt sync clocks with different skews. Is there an example for latch borrowing for async clocks?

5) How can we generate a divide by 3 clock without using negedge flop. I thought i can put an inverter on the clock and then use the inverted clock further. But can we put an inverter on the clock while writing rtl? I thought we should not touch clocks at all in our design except for gating them.

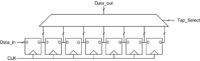

6) How do we implement 4 deep fifo using f/f? :sad:

7) Is the reset recovery and removal time only for flops with async resets with sync deassertion or is it for reset synchronizer flops as well? How do we take care of metastability in async flops?

8) I think we cannot have a totally glitchfree circuit. So what do we do to meet the timing. If I have a glitchy logic which meets the timing, is it ok? Can i live with such a design or is there a probability that my circuit my go into metastability anytime?

I am facing difficulty in understanding certain concepts.

Could you please clarify my following doubts:

1) Is there any example of having an intentional combo loop in design? Can combo loops be useful? How does synthesis tool and gate level simulation act on combo loop. How do we meet timings of combo loops?

2) How do we meet timings of mux? Do we need to do setcase analysis at all select inputs of mux or does synthesis tool do it for us?

3) Can we have useful latches in our design? Can we use it at any other place than during DFT?

4) The latch borrowing concept...i see it written that it is for fixing hold problems. Latch borrowing is done to increase the sampling time to half clock period, then how does it fix the hold issue? Doesnt it mean increasing the time for setup?

The latch borrowing concept that i have seen is wrt sync clocks with different skews. Is there an example for latch borrowing for async clocks?

5) How can we generate a divide by 3 clock without using negedge flop. I thought i can put an inverter on the clock and then use the inverted clock further. But can we put an inverter on the clock while writing rtl? I thought we should not touch clocks at all in our design except for gating them.

6) How do we implement 4 deep fifo using f/f? :sad:

7) Is the reset recovery and removal time only for flops with async resets with sync deassertion or is it for reset synchronizer flops as well? How do we take care of metastability in async flops?

8) I think we cannot have a totally glitchfree circuit. So what do we do to meet the timing. If I have a glitchy logic which meets the timing, is it ok? Can i live with such a design or is there a probability that my circuit my go into metastability anytime?