roki

Member level 1

Hi everyone,

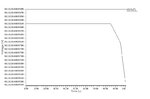

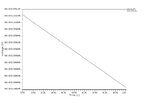

Attached above is the transient result of my LDO with output of 0.9V. The first figure is at 0oC, the second is at 27oC and the third is 85oC.

For 1st figure, the output is very distorted.

For 2nd figure, the is a sudden glitch at the front.

For 3rd figure, the output is going down.

I'm supposed to get a straight constant value.But I do not know the reason of why my results are shaped like that, so please help me understand.Is it parasitic oscillation? if yes, what causes it?

Thank you!

Regards

Last edited: