frilance

Member level 1

Hi guys!

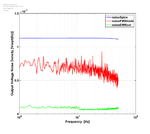

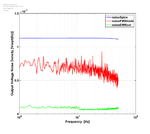

I wanted to compare the simulated noise in LTSpice with the experimental result measured using a Spectrum Analyzer (hp4395A) and I built the circuit you can see in the attached picture.

The 50 Ohms load in the LTspice simulation represents the input impedance of the Spectrum Analyzer.

But as you can see in the Matlab plot of the output data, both results differ quite a lot (LTSpice in the order of 110 nV/sqrt(Hz) and around 60-70 nV/sqrt(Hz) in the Spectrum Analyzer)

I don't know what could cause this discrepancy. Are the spice models that bad? Am I doing something wrong in the simulation? The attenuation of the Spectrum Analyzer was set to 0 dB.

Thanks a lot in advance.

Cheers!

I wanted to compare the simulated noise in LTSpice with the experimental result measured using a Spectrum Analyzer (hp4395A) and I built the circuit you can see in the attached picture.

The 50 Ohms load in the LTspice simulation represents the input impedance of the Spectrum Analyzer.

But as you can see in the Matlab plot of the output data, both results differ quite a lot (LTSpice in the order of 110 nV/sqrt(Hz) and around 60-70 nV/sqrt(Hz) in the Spectrum Analyzer)

I don't know what could cause this discrepancy. Are the spice models that bad? Am I doing something wrong in the simulation? The attenuation of the Spectrum Analyzer was set to 0 dB.

Thanks a lot in advance.

Cheers!