delta136

Newbie level 5

- Joined

- Dec 5, 2014

- Messages

- 10

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 84

Hey everyone! Would greatly appreciate it if someone could look over my code and tell me if I implemented this correctly.

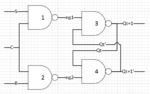

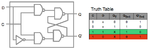

1-bit SR-Latch: (Teacher provided the diagram and truth table)

Code here: (c is for the clock)

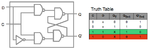

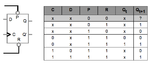

1-bit D-Latch:

Code here:

The reason I ask for someone to look over it is because I'm not sure if my code reproduces the two truth tables.

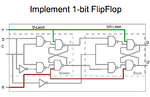

And lastly, the ultimate goal is to use the SR-latch and D-latch to make a Flip Flop (That's a D-Flip Flop, right?)

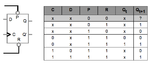

Can someone explain to me what the 'P' is in the flip flop? Why does the truth table contain only Q and not Q' like the above pictures, yet the output of the flip flop has Q and Q'?

Thank you very much for your time and help!

1-bit SR-Latch: (Teacher provided the diagram and truth table)

Code here: (c is for the clock)

Code Verilog - [expand]

1-bit D-Latch:

Code here:

Code Verilog - [expand]

The reason I ask for someone to look over it is because I'm not sure if my code reproduces the two truth tables.

And lastly, the ultimate goal is to use the SR-latch and D-latch to make a Flip Flop (That's a D-Flip Flop, right?)

Can someone explain to me what the 'P' is in the flip flop? Why does the truth table contain only Q and not Q' like the above pictures, yet the output of the flip flop has Q and Q'?

Thank you very much for your time and help!

Last edited by a moderator: