amsdesign

Member level 3

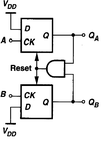

I am designing a phase frequency detector for a PLL using the standard configuration as shown below.

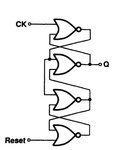

Each D FF is implemented as shown below:

Can you tell me how I can determine the maximum operating frequency of each Flip flop?

Also, how do the sizing of the CMOS pairs in each gate affect the frequency?

Each D FF is implemented as shown below:

Can you tell me how I can determine the maximum operating frequency of each Flip flop?

Also, how do the sizing of the CMOS pairs in each gate affect the frequency?