livecf

Newbie level 5

Hi all,

I'm using a transmission gate base DFF to build a simple frequency divider. It worked, but I'm getting some weird waveform at some intermediate nodes and the power consumption is high too (11uW). Could anyone kind enough to provide some insights on this problem.

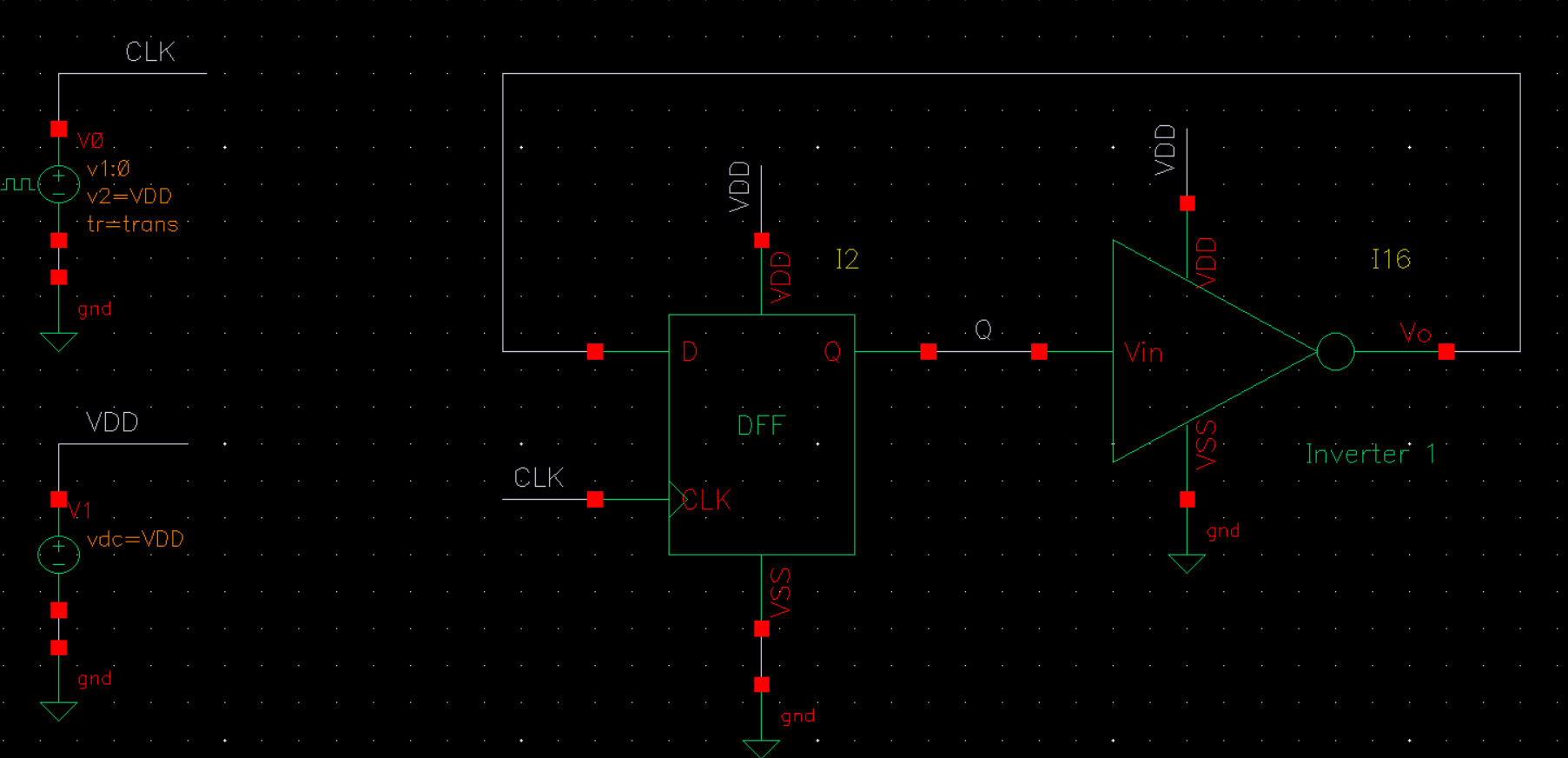

Here is the testbench, I'm using 1.8V VDD and 100kHz clock.

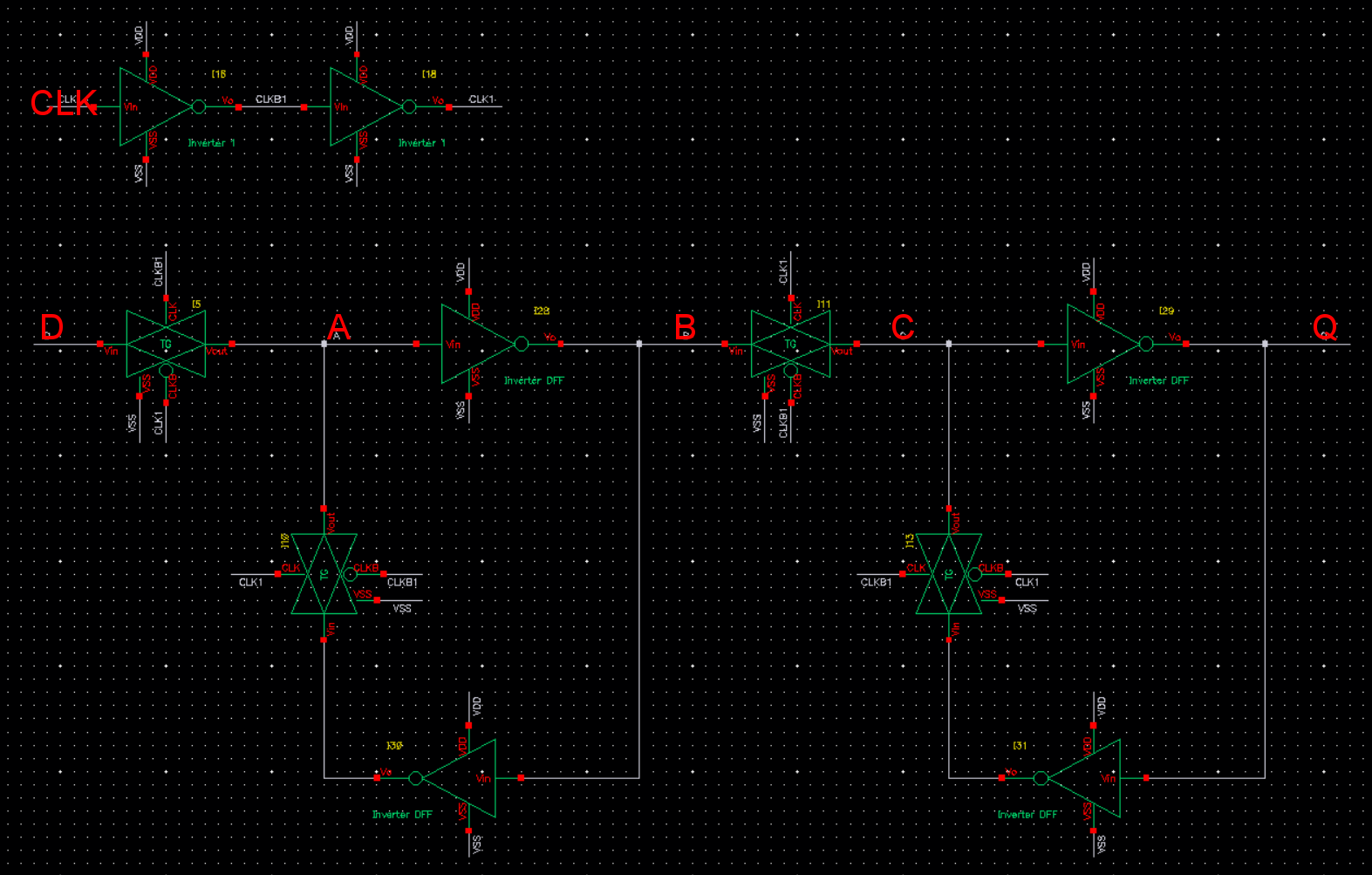

Here is the DFF sch:

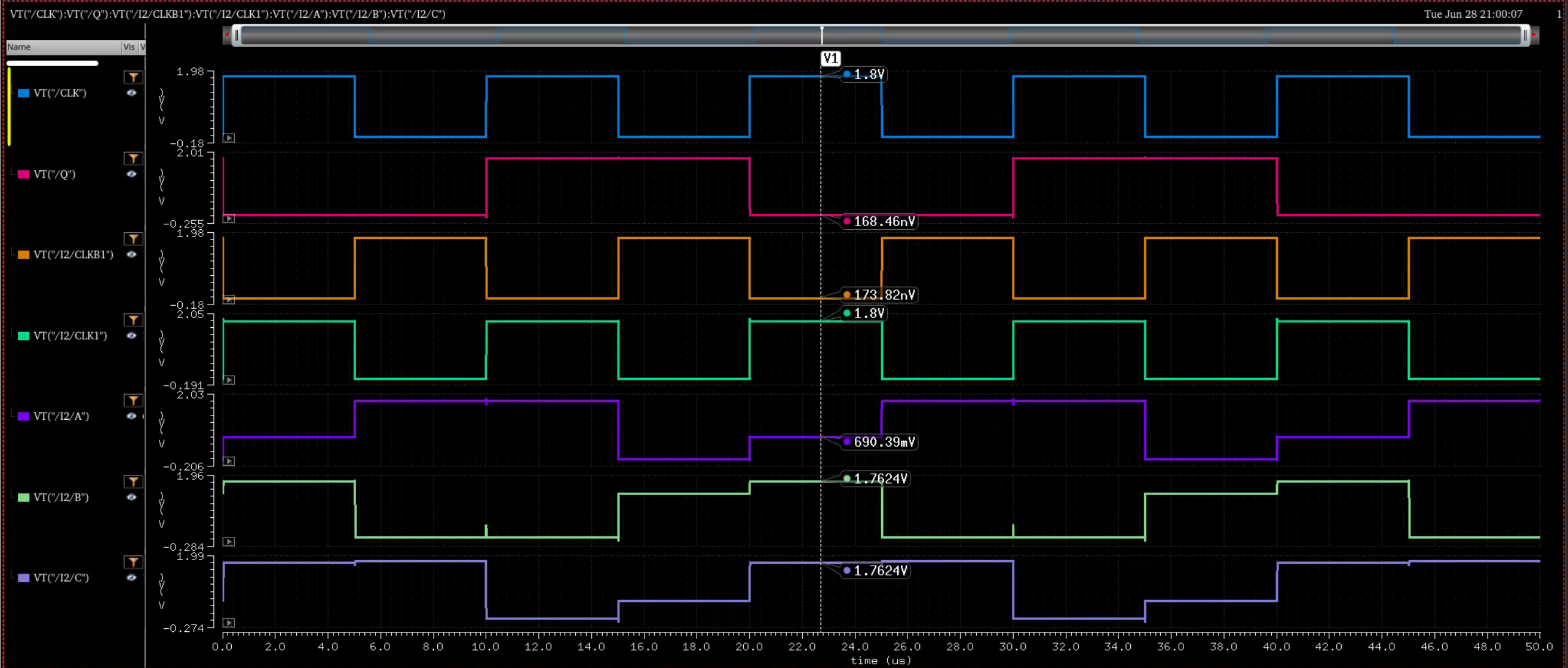

Here is the waveform, you can see I have some weird staircase like waves in some nodes.

I'm using a transmission gate base DFF to build a simple frequency divider. It worked, but I'm getting some weird waveform at some intermediate nodes and the power consumption is high too (11uW). Could anyone kind enough to provide some insights on this problem.

Here is the testbench, I'm using 1.8V VDD and 100kHz clock.

Here is the DFF sch:

Here is the waveform, you can see I have some weird staircase like waves in some nodes.