Lizwi

Newbie

Hi

I am simulating a time to digital converter using Verilog in Quartus. It consists of both coarse and fine measurement. I have already simulated counter using structural modelling.

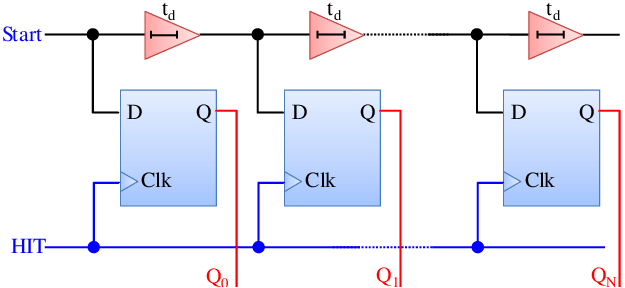

Please help me with a code to simulate a tapped delay line like in the picture. The buffers must have a delay. Please please help me.

I am simulating a time to digital converter using Verilog in Quartus. It consists of both coarse and fine measurement. I have already simulated counter using structural modelling.

Please help me with a code to simulate a tapped delay line like in the picture. The buffers must have a delay. Please please help me.