yefj

Advanced Member level 4

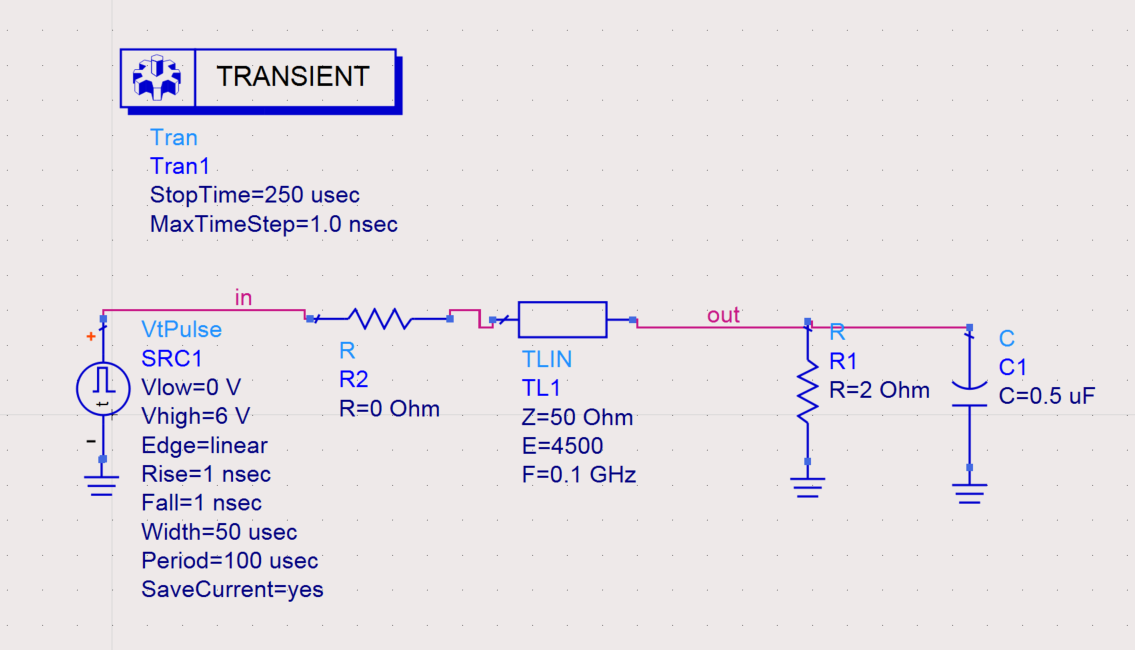

Hello,I am trying to simulate the effect of improving a square pulse with decoupling capacitors.

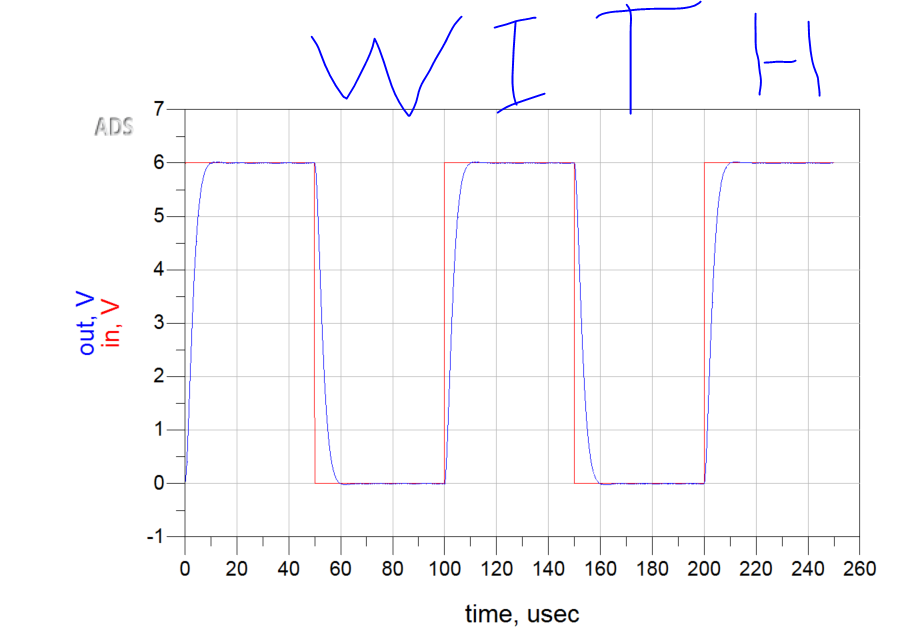

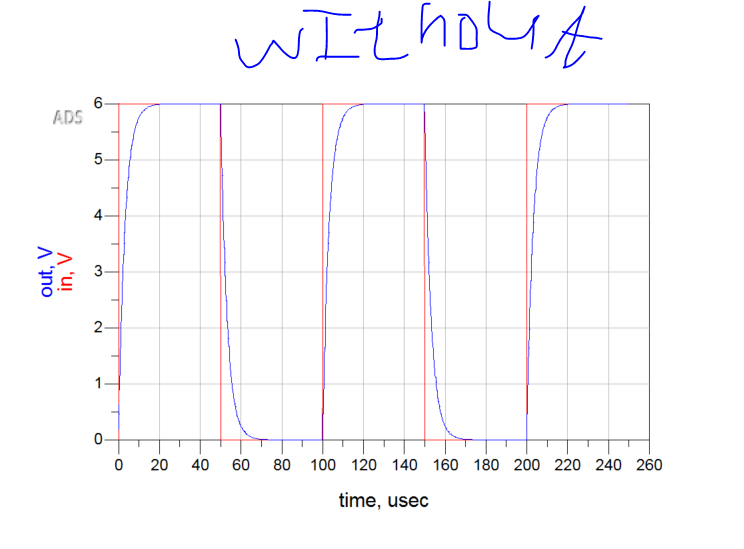

One plot i with 0.5uF on the load and the other is without .The capacitor didn't help much with improving the pulse on the load to be as close as possible to the input one.

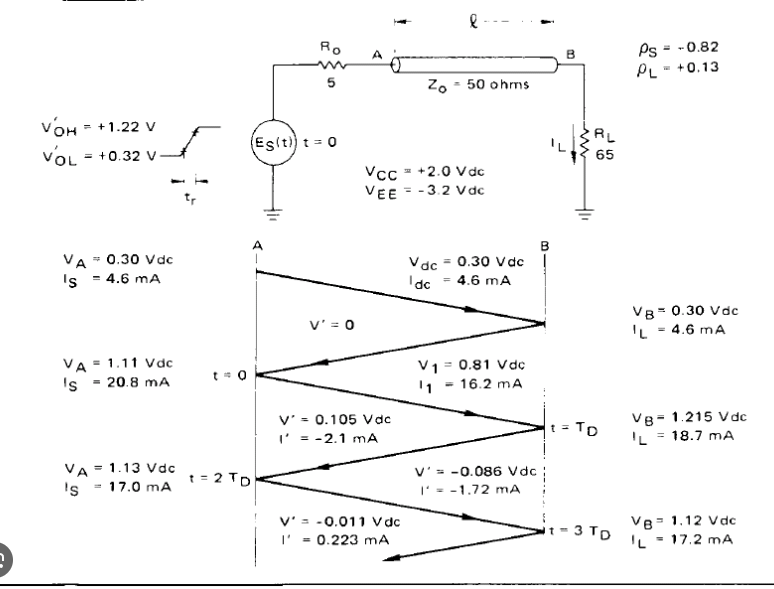

i know that the result on the load is a sum of reflected waves going back and forth.

is there a way based on transmission line reflection theory to know what decoupling capacitors should i use to deliver a signal as close as it was at the input?

Thanks.

One plot i with 0.5uF on the load and the other is without .The capacitor didn't help much with improving the pulse on the load to be as close as possible to the input one.

i know that the result on the load is a sum of reflected waves going back and forth.

is there a way based on transmission line reflection theory to know what decoupling capacitors should i use to deliver a signal as close as it was at the input?

Thanks.