yefj

Advanced Member level 4

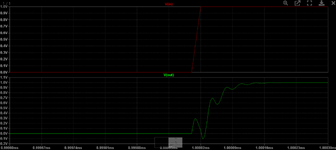

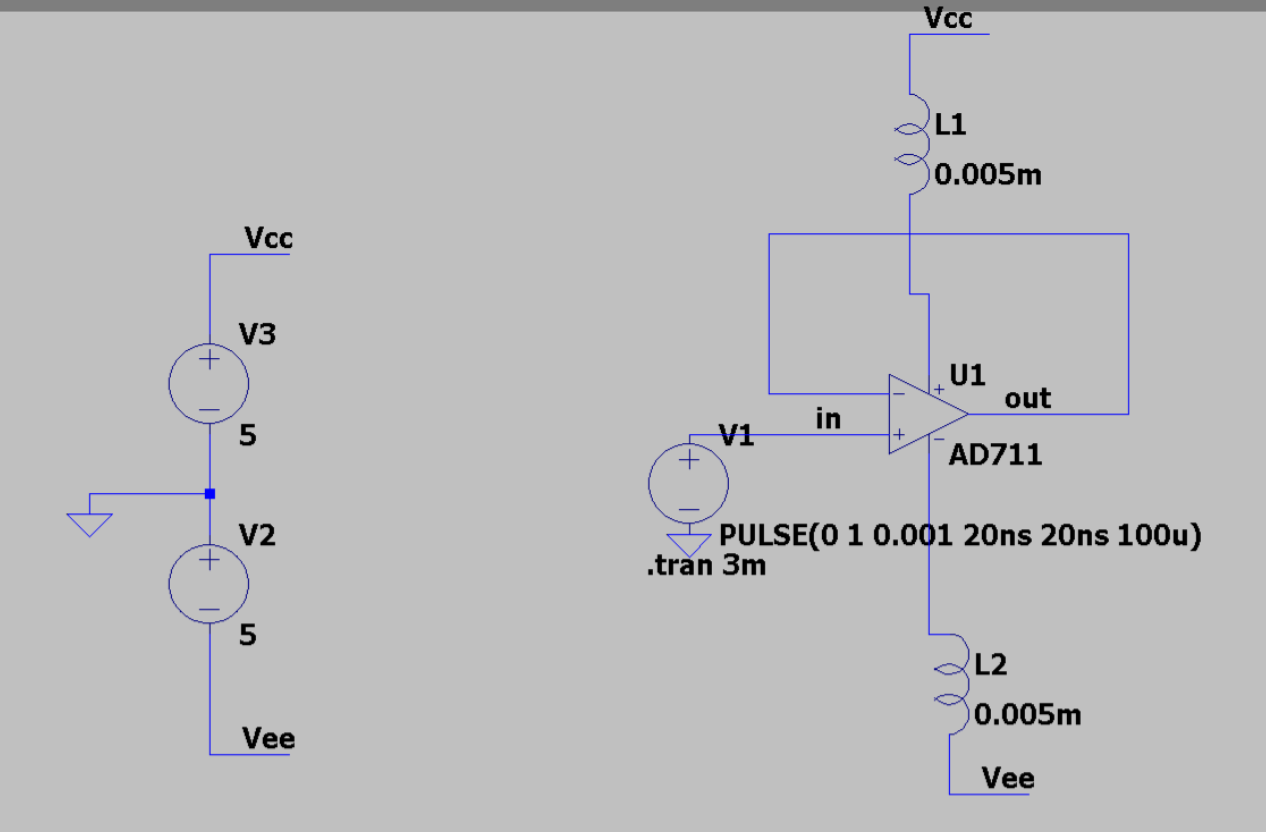

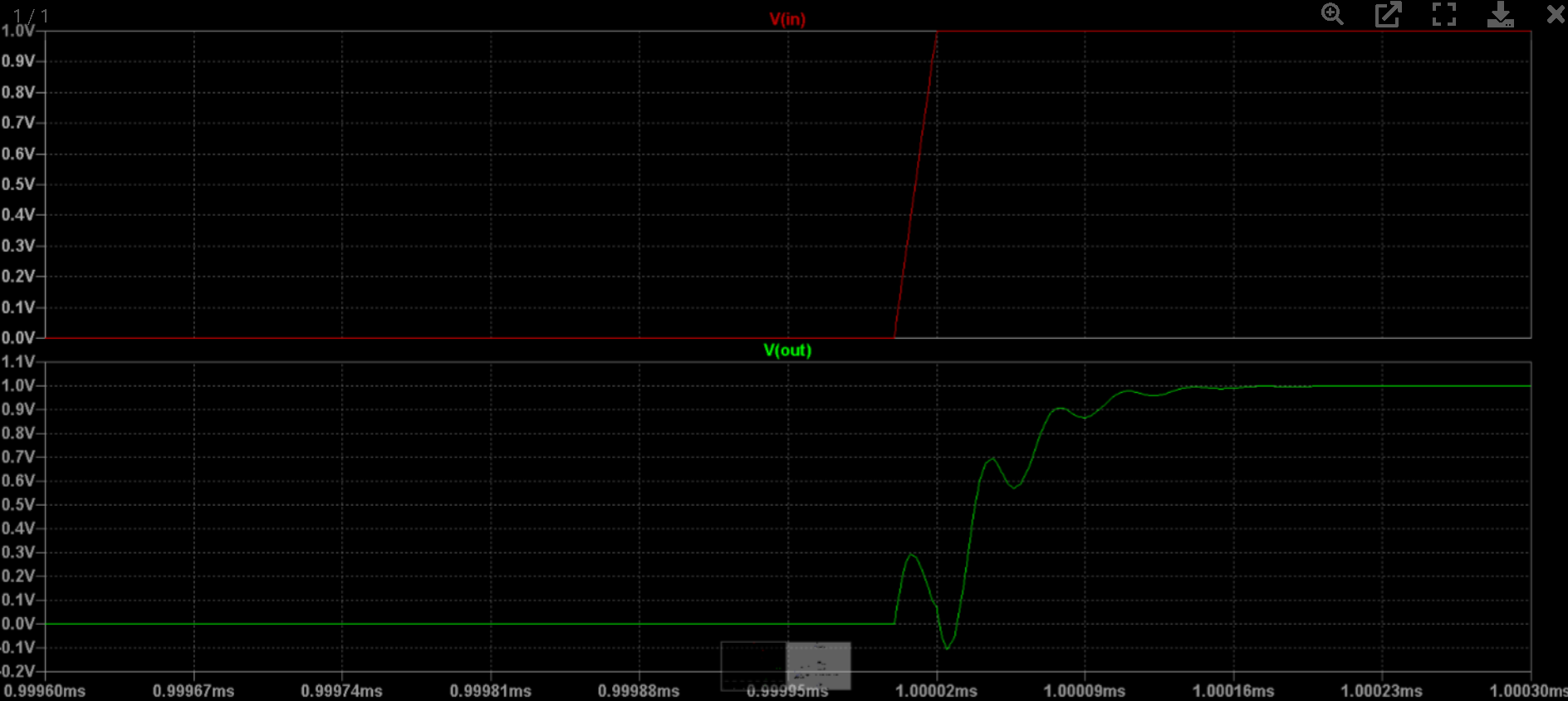

Hello , I have a pulse signal going into a buffer, L1 and L2 represent bad PCB power delivery network to this buffer.

the goal of a good PDN network that we will not have HIGH impedance between Vcc and GND.

sudden change of input can cause sudden change of DC current consumption.

i want to improve the situation so my pulse signal with pass without destortions shown bellow.

I know i need to plan the PDN according to the impedance profile at some frequency range.

I know my pulse can be viewed at frequency responce usint FFT.

Could you please say at what frequency range i need to plan my PDN?

Thanks.

the goal of a good PDN network that we will not have HIGH impedance between Vcc and GND.

sudden change of input can cause sudden change of DC current consumption.

i want to improve the situation so my pulse signal with pass without destortions shown bellow.

I know i need to plan the PDN according to the impedance profile at some frequency range.

I know my pulse can be viewed at frequency responce usint FFT.

Could you please say at what frequency range i need to plan my PDN?

Thanks.