yuvalkesi

Member level 5

Hi,

I'm writing a ddr1 controller in VHDL (novice @ ddr, but read the spec and the data sheet), and having a hard time understanding the clocks on the system

Please see in this link, page 3:

**broken link removed** (btw, I know Lattice have a controller based on this data sheet, I just want to do it by mysetlf).

I've also attached the picture (1). I don't understand what is the difference between clk and ddr_clk. Let's say we're talking about ddr266 (so the clock freq is 133MHz). Which is the 133MHz? clk, or ddr clk? which is 90deg phase?

I've tried also in altera to find some answers...

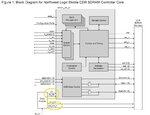

Mobile DDR SDRAM Controller Core

See picture attached (2). There's also 2 kinds of clocks (clk and ext_clk). What is the difference between them?

I have 50MHz clock on my board. I understand I need to make a 133MHz clock out of it using a PLL (inside my Cyclone II). But what are all these clock used for?

Thank you!!!

Tom

I'm writing a ddr1 controller in VHDL (novice @ ddr, but read the spec and the data sheet), and having a hard time understanding the clocks on the system

Please see in this link, page 3:

**broken link removed** (btw, I know Lattice have a controller based on this data sheet, I just want to do it by mysetlf).

I've also attached the picture (1). I don't understand what is the difference between clk and ddr_clk. Let's say we're talking about ddr266 (so the clock freq is 133MHz). Which is the 133MHz? clk, or ddr clk? which is 90deg phase?

I've tried also in altera to find some answers...

Mobile DDR SDRAM Controller Core

See picture attached (2). There's also 2 kinds of clocks (clk and ext_clk). What is the difference between them?

I have 50MHz clock on my board. I understand I need to make a 133MHz clock out of it using a PLL (inside my Cyclone II). But what are all these clock used for?

Thank you!!!

Tom