mretsh91

Junior Member level 3

- Joined

- Jan 26, 2013

- Messages

- 28

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Activity points

- 1,509

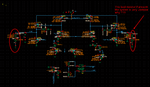

I am working on a 2 stage fully differential op amp, but I have a problem with the CMFB ...please I need help with the suitable CMFB ??? I believe that I need only 1 cmfb block that will adjust both stages ,,,but I don't know the suitable technique ...I want to apply it now only using ideal vcvs and sensing using resistors ...just behavioral

thanks in advance

thanks in advance