naspek

Member level 1

Hey there.. I've got couple of questions need to be answer.. i really got no idea to solve it..

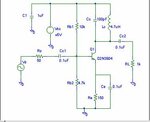

1) During DC biasing measurement, if CE changes from 0.1 µF to 1 µF, what happen to the readings in VE (assume CE is ideal capacitor, no parasitic resistance or inductance)?

2) The input and output (VB and VL) waveform should be approximately 180° out of phase during resonance. VB is leading VL or in reverse way? Why?

1) During DC biasing measurement, if CE changes from 0.1 µF to 1 µF, what happen to the readings in VE (assume CE is ideal capacitor, no parasitic resistance or inductance)?

2) The input and output (VB and VL) waveform should be approximately 180° out of phase during resonance. VB is leading VL or in reverse way? Why?