Teszla

Member level 2

- Joined

- Jun 6, 2013

- Messages

- 45

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Activity points

- 1,556

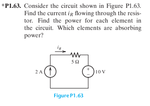

I wonder how this circuit configuration is possible. We have a voltage source of 10V, which (according to it's terminals) would induce a current in the counter-clockwise direction. Together with the resistance that would be a current of 2A counter-clockwise. However, we also have a current source which induces 2A in the other direction. Why doesn't these two cancel each other out?

Apparently the voltage source can also absorb power, which means that it's voltage would be in the other direction. But wouldn't it then be -10 V?

When applying KVL, the current source together with the resistance would be 2A*5Ohm=10V. For KVL to be correct, the voltage source then has to equal -10 V, wouldn't it? Might the "10V" written next to the voltage source be a misprint or is there any reason they didn't write a minus?