allennlowaton

Full Member level 5

Good day to all.

I would to ask for any suggestions and ideas regarding this.

The output of charge pump without a switch is 3.85V which is already enough for my application). However, when there's a PMOS switch already

it's output become 3.25V. There's a 0.6V drop.

I want the CP output to be as high as possible.

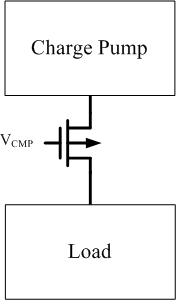

Shown below is the figure of charge pump, switch and the load.

Thank you.

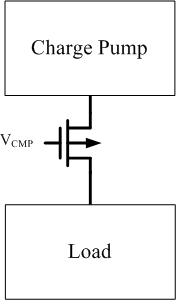

I would to ask for any suggestions and ideas regarding this.

The output of charge pump without a switch is 3.85V which is already enough for my application). However, when there's a PMOS switch already

it's output become 3.25V. There's a 0.6V drop.

I want the CP output to be as high as possible.

Shown below is the figure of charge pump, switch and the load.

Thank you.