Hatmpatn

Member level 3

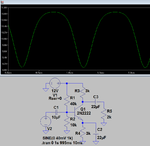

So it should be R4=(12-5.16667)/0.004=1708.3325Ω

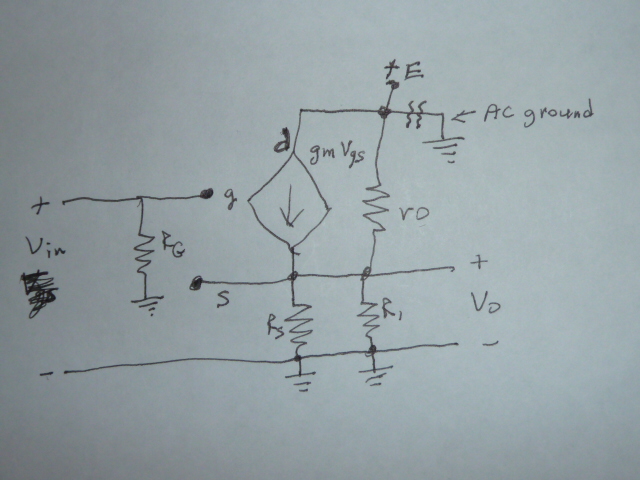

So if I get you right I should take the derivative of iD=IDSS*(1-uGS/Up)² with respect to uGS.

With the given values inserted this equals: 0.00514286+0.00146939uGS, when I put my uGS in it, it gives me gm=0.00342857=3.4286mS

Haha, it's the same(but positive)! Sick!

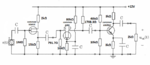

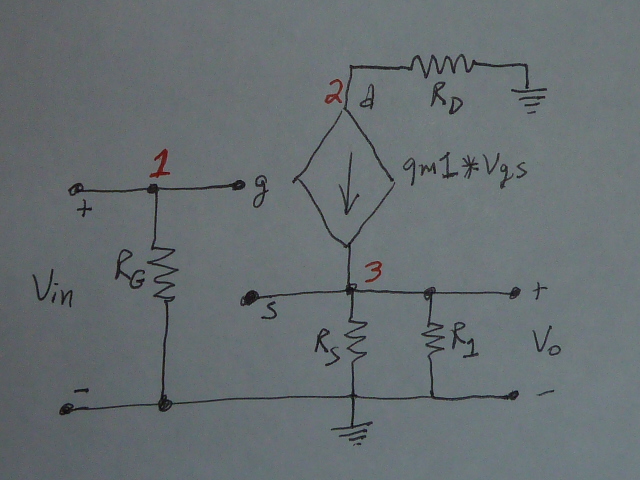

How do I calculate the operating point of the first FET?

So if I get you right I should take the derivative of iD=IDSS*(1-uGS/Up)² with respect to uGS.

With the given values inserted this equals: 0.00514286+0.00146939uGS, when I put my uGS in it, it gives me gm=0.00342857=3.4286mS

Haha, it's the same(but positive)! Sick!

How do I calculate the operating point of the first FET?

Last edited: