Rimvis123

Junior Member level 2

hello everyone,

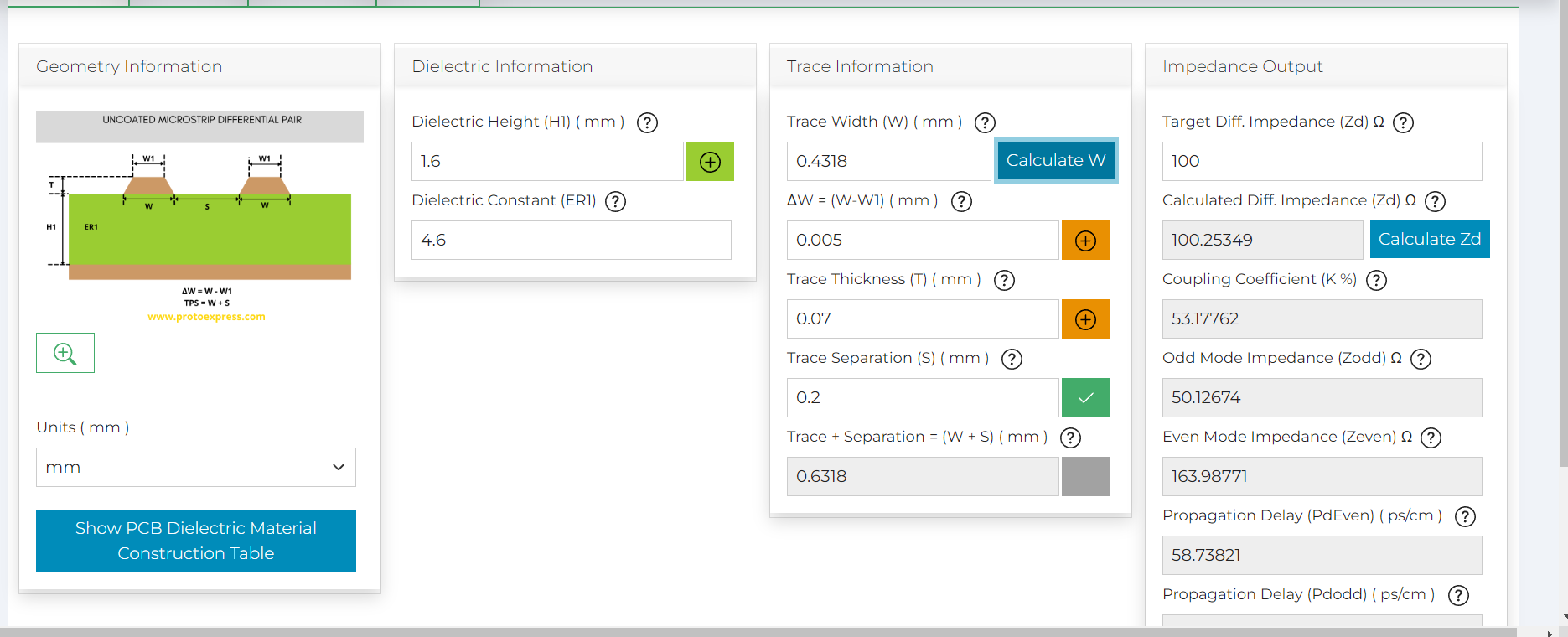

I do not understand how to calculate diff pairs with saturn or Sierra circuits programs. I need to route 100ohm (this line is from crystal oscillator to microcontroller so 100 ohm is right yes?) impedance diff pair line. I'm trying to calculate it, but I don't understand what dielectric height, ΔW and Trace Thickness (T) ( mm ) I need to put. In dielectric height I need put 1,6mm as my full pcb height or height between top and second layer?

I do not understand how to calculate diff pairs with saturn or Sierra circuits programs. I need to route 100ohm (this line is from crystal oscillator to microcontroller so 100 ohm is right yes?) impedance diff pair line. I'm trying to calculate it, but I don't understand what dielectric height, ΔW and Trace Thickness (T) ( mm ) I need to put. In dielectric height I need put 1,6mm as my full pcb height or height between top and second layer?