royo.oreo

Newbie

Hi all,

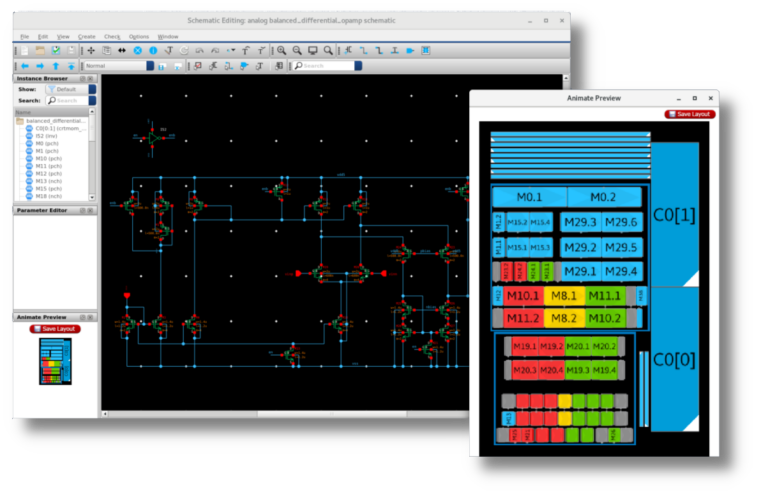

I am using Virtuoso IC6.1.6 and I have spent the past couple of days trying to find a tutorial to convert a schematic into a layout. My project is a high speed SERDES serial link and I have finally finished all the simulations and I am now ready for layout.

Thing is, I am using schematic view to design my entire project and I am wondering if there is any tutorial to convert my huge design into a layout. I've tried searching through the web for tutorials but most of them are manual routing and manual placements which would not be ideal for my situation.

I tried:

1. Launch -> Layout XL -> Connectivity -> Generate from all sources.

2. Connectivity -> Place as in schematic

3. Routing -> automatic router.

It seems this method is far from ideal since placement is not optimal and the automatic router is not perfect and causes some DRC errors. While I looked through the web, most Layout XL tutorials are mostly manual and it is not suitable for my needs since I will not be able to manually route my entire design. Please let me know if there is anything else I can do!

Thanks for reading.

I am using Virtuoso IC6.1.6 and I have spent the past couple of days trying to find a tutorial to convert a schematic into a layout. My project is a high speed SERDES serial link and I have finally finished all the simulations and I am now ready for layout.

Thing is, I am using schematic view to design my entire project and I am wondering if there is any tutorial to convert my huge design into a layout. I've tried searching through the web for tutorials but most of them are manual routing and manual placements which would not be ideal for my situation.

I tried:

1. Launch -> Layout XL -> Connectivity -> Generate from all sources.

2. Connectivity -> Place as in schematic

3. Routing -> automatic router.

It seems this method is far from ideal since placement is not optimal and the automatic router is not perfect and causes some DRC errors. While I looked through the web, most Layout XL tutorials are mostly manual and it is not suitable for my needs since I will not be able to manually route my entire design. Please let me know if there is anything else I can do!

Thanks for reading.