AllenD

Member level 5

Hi Team

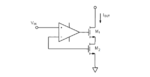

As is known to many people, a common drain circuit can be used as a voltage shifter since it's gain~=1 and the input-output dc voltage is shifted by Vgs=Vth+Vdsat.

It came to me that what if Vgs is too big? If I only want to shift the DC level by 0.5*Vgs, is there a convenient circuit to use?

Thanks

Allen

As is known to many people, a common drain circuit can be used as a voltage shifter since it's gain~=1 and the input-output dc voltage is shifted by Vgs=Vth+Vdsat.

It came to me that what if Vgs is too big? If I only want to shift the DC level by 0.5*Vgs, is there a convenient circuit to use?

Thanks

Allen