alimassster

Junior Member level 3

Hello friends

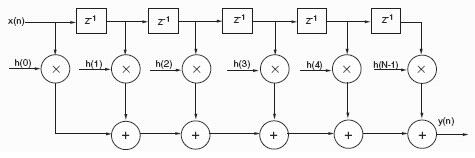

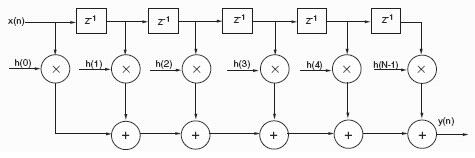

Imagine x as a continuous stream of input samples and y as a resulting stream

the sample delay logic is denoted by Z**-1, where the -1 represents a single clock delay.The delayed input samples are supplied to one input of the multiplier.coefficients (denoted by h0 to h(N-1)) are supplied to the other input of the multiplier Y is merely the summation of a set of input samples.

is merely the summation of a set of input samples.

Now my question

How many clocks do we need to have a result in the output?

And if we need for example N clocks to feed multipliers with N inputs in a N tap FIR filter to calculate Y , then what's the difference between the parallel form and a single MACC based form ( there's an equal delay(number of clocks) in both forms)?

thx

Imagine x as a continuous stream of input samples and y as a resulting stream

the sample delay logic is denoted by Z**-1, where the -1 represents a single clock delay.The delayed input samples are supplied to one input of the multiplier.coefficients (denoted by h0 to h(N-1)) are supplied to the other input of the multiplier Y

Now my question

How many clocks do we need to have a result in the output?

And if we need for example N clocks to feed multipliers with N inputs in a N tap FIR filter to calculate Y , then what's the difference between the parallel form and a single MACC based form ( there's an equal delay(number of clocks) in both forms)?

thx