metalmisers

Junior Member level 2

Hello everyone,

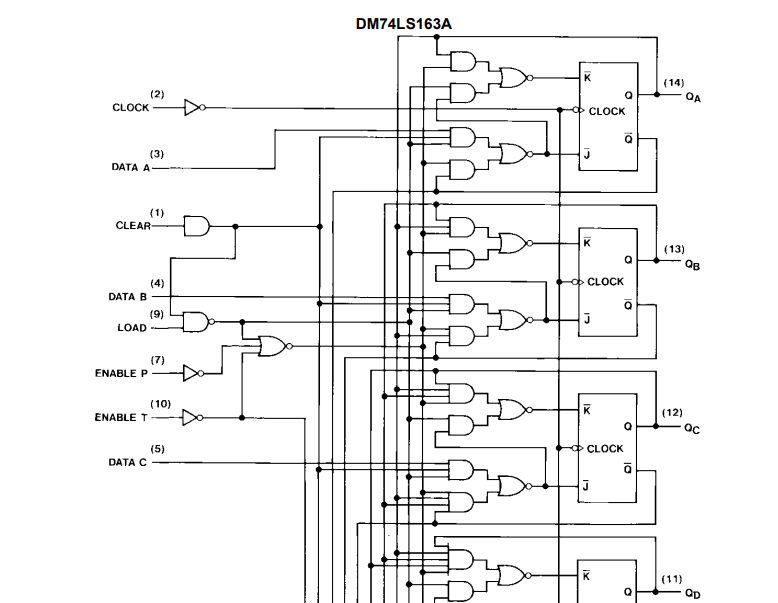

I am trying to replicate the DM74LS163A in VHDL but as we can see in the attached file, the J and K inputs have bars on top, does this mean they are logically inverted?

Any help will be greatly appreciated.

I am trying to replicate the DM74LS163A in VHDL but as we can see in the attached file, the J and K inputs have bars on top, does this mean they are logically inverted?

Any help will be greatly appreciated.