itayd100

Junior Member level 3

Hey E-design,

First, I appreciate your help!

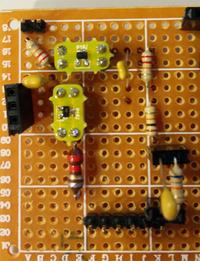

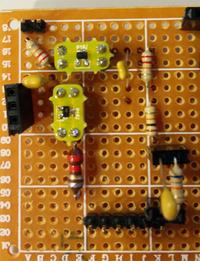

I built the circuit on a proto-board with 2 BAT54WT1G (see the pic).

I see that you got a good result, I'll try to see if I did a mistake. Anyway, I'll order it on a PCB.

Second, I tried to connect it to HCMOS clock 66.66 MHz with 3Vpp and get the amplitude, but I get weird results. The Vpp of the peak detector getting (much) bigger. Do you have any idea? (or it is just me ;-) )

BAT54:

https://nl.farnell.com/on-semicondu...categorieën&categoryNameResp=Alle+categorieën

HCMOS:

https://www.farnell.com/datasheets/75480.pdf

First, I appreciate your help!

I built the circuit on a proto-board with 2 BAT54WT1G (see the pic).

I see that you got a good result, I'll try to see if I did a mistake. Anyway, I'll order it on a PCB.

Second, I tried to connect it to HCMOS clock 66.66 MHz with 3Vpp and get the amplitude, but I get weird results. The Vpp of the peak detector getting (much) bigger. Do you have any idea? (or it is just me ;-) )

BAT54:

https://nl.farnell.com/on-semicondu...categorieën&categoryNameResp=Alle+categorieën

HCMOS:

https://www.farnell.com/datasheets/75480.pdf