Ans5671

Member level 2

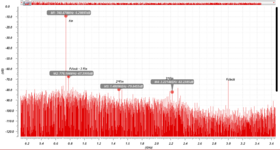

I am simulating a DAC at 3GHz. The SFDR for different frequencies is as follows.

@ 100MHz = 67 dB

@ 700MHZ = 52 dB

@1.47GHz = 60 dB

I do not understand why the SFDR drops for middle frequencies. I have attached the graph for reference.

The Fclock - 3 * Fin amplitude is more than the 3 Fin. Why?

The spectrum is taken for 4096 clock cycles and 4096 * 128 point FFT of the transient output.

Thank you

@ 100MHz = 67 dB

@ 700MHZ = 52 dB

@1.47GHz = 60 dB

I do not understand why the SFDR drops for middle frequencies. I have attached the graph for reference.

The Fclock - 3 * Fin amplitude is more than the 3 Fin. Why?

The spectrum is taken for 4096 clock cycles and 4096 * 128 point FFT of the transient output.

Thank you

Attachments

Last edited: