FEM33

Newbie

Hello everyone,

For my internship I need to prove why at the midcode, the DNL is the maximum.

I'm designing a 10 bit DAC.

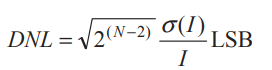

I need to express DNL and INL as a function of (sigmaI/I).

I_LSB = I_OUT_MAX/2^N -1

I found this on internet, maybe its true, but idk how to prove it

We need to start from the bottom with that equation :

DNL(k) =( (I(k) - I(k-1) )/I_LSB ) ) - 1

Thanks for all your answers :

For my internship I need to prove why at the midcode, the DNL is the maximum.

I'm designing a 10 bit DAC.

I need to express DNL and INL as a function of (sigmaI/I).

I_LSB = I_OUT_MAX/2^N -1

I found this on internet, maybe its true, but idk how to prove it

We need to start from the bottom with that equation :

DNL(k) =( (I(k) - I(k-1) )/I_LSB ) ) - 1

Thanks for all your answers :