bravoegg

Member level 2

the code in modelsim simlulation turns out to be different from signaltap waveform.

the idea is to set x to a certain value and keep it, when some condition is met.

like when wren_s == 1, then set x = 3 and keep it, unless another if-statement gets invoked.

modelsim simulation works excalty as I wanted, but the real signaltap waveform is different.

In signaltap waveform, when the if-statement condition is met, x is set to predefined value(which is what I want), but the circuit didn't keep the value, instead immediately change x's value to 262. Why would x be latched to 262?

Where did I get it wrong? Please help...Thanks in advance.

the idea is to set x to a certain value and keep it, when some condition is met.

like when wren_s == 1, then set x = 3 and keep it, unless another if-statement gets invoked.

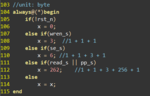

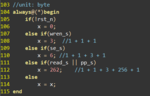

Code:

always@(*)begin

if(!rst_n)

x = 0;

else if(wren_s)

x = 3; //1 + 1 + 1

else if(se_s)

x = 6; //1 + 1 + 3 + 1

else if(read_s || pp_s)

x = 262; //1 + 1 + 3 + 256 + 1

else

x = x;

end

modelsim simulation works excalty as I wanted, but the real signaltap waveform is different.

In signaltap waveform, when the if-statement condition is met, x is set to predefined value(which is what I want), but the circuit didn't keep the value, instead immediately change x's value to 262. Why would x be latched to 262?

Where did I get it wrong? Please help...Thanks in advance.

Last edited: