engr_joni_ee

Advanced Member level 3

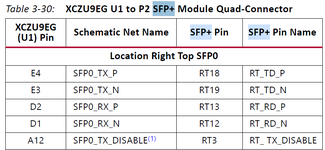

How we describe the signal between FPGA and SFP+ connector on the PCB traces. There are two differential pairs in SFP+ connector, one for Tx and the other is for Rx. What is the clock frequency and clock period of Tx and Rx signals between FPGA and SFP+ connector on the PCB traces ? If someone need to draw the waveform for understanding then which frequency and voltage level to use.