znoopie

Newbie level 3

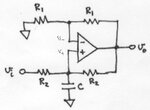

It is given that the input node vi has low impedance and the output node vo has high impedance. The question is "What does this circuit do?".

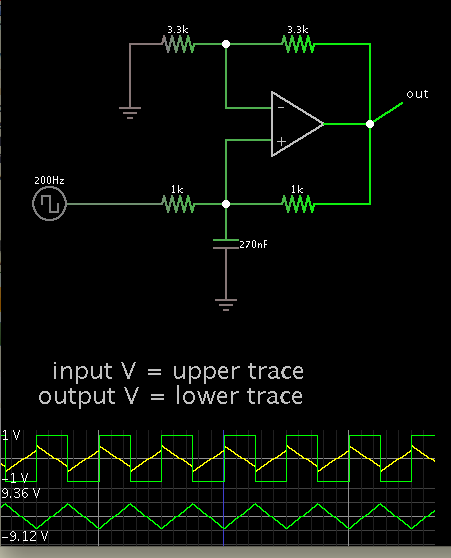

Assuming that op-amp's gain is very large, I computed the transfer function and got vo/vi = 2/(s*R2*C), which is an integrator or a low-pass filter.

However, I'm still skeptical about the information on the input/output impedance. I thought it would affect the circuit's function in some way. Help or comments are appreciated.

Thanks in advance.

Assuming that op-amp's gain is very large, I computed the transfer function and got vo/vi = 2/(s*R2*C), which is an integrator or a low-pass filter.

However, I'm still skeptical about the information on the input/output impedance. I thought it would affect the circuit's function in some way. Help or comments are appreciated.

Thanks in advance.