Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

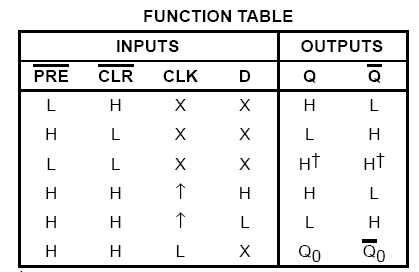

It is a classic example:

Code VHDL - [expand]

Code VHDL - [expand]

Code VHDL - [expand]

Code VHDL - [expand]

This was the reason why I answered with what would be done by real world engineers. Along with my comment about not hiring anyone who would write something like the code in #3 and #4.It is obvious that this is a school homework, so I would not normally answer, but I think the previous answers are confusing for a beginner.

Maybe the school wants you to design a single bit d-type flip flop and then instantiate it 8 times.

That is not how we do it in the real engineering world, but the core function will look like this, regardless of the number of bits:

Unfortunately given the lack of quality in the code snippets "out in the wild" they are likely to continue the trend of antiquated coding styles (the education system also seems to be behind the times based on the plethora of pre-2000 coding styles being used for both VHDL and Verilog.The rest of the code and the test bench is up to you. You will learn nothing if we give you the answer here. Use your VHDL book and Google to collect the information you need.

hello

please I need help in VHDl code Hex d flip flops with clear and testbench as well..... thanks

Then post the code that you've done that still doesn't work.Sorry.... I tried many times, but I could not could you help me please.

http://www.asic-world.com/examples/vhdl/d_ff.html

Yes. I'm completely with ads-ee in this regardI mean HEX D flip flops with clear.... not d-type flip flop register with clock enable not the same.

You should be able to extrapolate how to write a hex D-FF with clear instead of an enable from post #6 or #7. If you can't then you could perform a search on google.