Raeiu

Newbie level 5

Hi everyone, first of all sorry for my bad english.

I have a problem with this code. It generates a csv file where writes stimuli for a TB (external).

It writes a first line of text with signals name, in the second line should write the first test case (text), after this writes signals and then: second test case, signals, third test case ecc.

An example of what i would like to achieve:

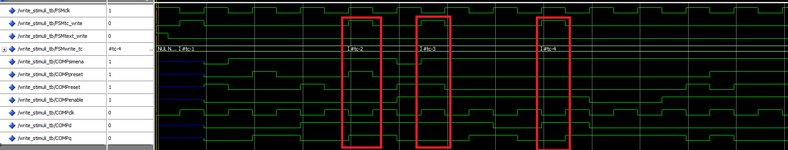

But it "skip" the second line of text: it writes a line of signals and after #TC-1 and i don't understand why. (see attach file)

For write test cases texts i used a process that, when the signal test_case is '1', signal tc_write write the line, test_case turn '0', wait for xx ns, and then the signals (surely there is a better way to do this).

I hope I was clear in my explanation.

I have a problem with this code. It generates a csv file where writes stimuli for a TB (external).

It writes a first line of text with signals name, in the second line should write the first test case (text), after this writes signals and then: second test case, signals, third test case ecc.

An example of what i would like to achieve:

| #simENA | D | Reset | Enable | CLK |

| #TC-1 | ||||

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| ... | ... | ... | ... | ... |

| #TC-2 | ||||

| ... | ... | ... | ... | ... |

| #TC-3 | ||||

| ... | ... | ... | ... | ... |

For write test cases texts i used a process that, when the signal test_case is '1', signal tc_write write the line, test_case turn '0', wait for xx ns, and then the signals (surely there is a better way to do this).

I hope I was clear in my explanation.

Code:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_TEXTIO.ALL;

USE STD.TEXTIO.ALL;

USE STD.ENV.STOP;

ENTITY write_stimuli IS

END write_stimuli;

ARCHITECTURE RTL OF write_stimuli IS

SIGNAL simCLK : STD_LOGIC; --simulation clk

SIGNAL simENA : STD_LOGIC; --simulation enable. It's used on tb (external)

SIGNAL write_tc : STRING(1 TO 32);

SIGNAL test_case: STD_LOGIC;

--*************************************************************************************

-- FUNCTION STRING PAD

--*************************************************************************************

FUNCTION PADDED_STRING(s: STRING; n: POSITIVE) RETURN STRING IS

VARIABLE ps: STRING(1 TO n) := (OTHERS => ' ');

BEGIN

IF s'LENGTH >= n THEN

ps := s(1 TO n); --- truncate string

ELSE

ps(1 TO s'LENGTH) := s;

ps(s'LENGTH + 1 TO n) := (OTHERS => ' ');

END IF;

RETURN ps;

END;

--*************************************************************************************

-- PROCEDURE

--*************************************************************************************

PROCEDURE PWRITE(VARIABLE l: INOUT LINE; msg: IN STRING) IS

VARIABLE tab : CHARACTER := ';';

BEGIN

WRITE(l, msg);

WRITE(l, tab);

END PROCEDURE;

PROCEDURE PWRITE(VARIABLE l: INOUT LINE; sig: IN STD_LOGIC) IS

VARIABLE tab : CHARACTER := ';';

BEGIN

WRITE(l, sig);

WRITE(l, tab);

END PROCEDURE;

PROCEDURE TCWRITE(VARIABLE l: INOUT LINE; sig: IN STRING; FILE f: TEXT) IS

VARIABLE tab : CHARACTER := ';';

BEGIN

WRITE(l, sig);

WRITE(l, tab);

WRITELINE(f, l);

END PROCEDURE;

--*************************************************************************************

-- DICHIARAZIONE DEI SEGNALI

--

-- In questa sezione bisogna scrivere i segnali preceduti dal prefisso

-- "my". Questi sono i segnali necessari per la simulazione.

--*************************************************************************************

SIGNAL reset : STD_LOGIC;

SIGNAL enable : STD_LOGIC;

SIGNAL clk : STD_LOGIC;

SIGNAL D : STD_LOGIC;

SIGNAL Q : STD_LOGIC;

BEGIN

write_process: PROCESS

FILE stimulus : TEXT OPEN WRITE_MODE IS ("Stimoli.csv");

VARIABLE lo : LINE;

VARIABLE tab : CHARACTER := ';';

VARIABLE text_done : BOOLEAN := FALSE;

VARIABLE cont : natural := 1;

BEGIN

IF (text_done = FALSE) THEN -- Write first line on csv

PWRITE(lo, "#simENA");

PWRITE(lo, "D");

PWRITE(lo, "reset");

PWRITE(lo, "enable");

PWRITE(lo, "clk");

PWRITE(lo, "EXPECTED");

PWRITE(lo, "Q");

PWRITE(lo, "RESULT");

WRITELINE(stimulus, lo);

text_done := TRUE;

END IF;

IF (text_done = TRUE) THEN -- write test case

IF (test_case = '1') THEN

TCWRITE(lo, write_tc, stimulus);

END IF;

END IF;

IF (text_done = TRUE) THEN -- Write signals on csv

WAIT UNTIL simCLK <= '1';

PWRITE(lo, simENA);

PWRITE(lo, D);

PWRITE(lo, reset);

PWRITE(lo, enable);

PWRITE(lo, clk);

PWRITE(lo, string'(" "));

PWRITE(lo, Q);

PWRITE(lo, string'(" "));

WRITELINE(stimulus, lo);

cont := cont + 1;

IF (cont = 30) THEN

FILE_CLOSE(stimulus);

STOP;

END IF;

END IF;

END PROCESS;

--*************************************************************************************

-- SIGNAL PROCESS

--*************************************************************************************

simENA_process: PROCESS

BEGIN

simENA <= '0';

WAIT FOR 10 ns;

simENA <= '1';

WAIT FOR 70 ns;

simENA <= '0';

WAIT FOR 10 ns;

simENA <= '1';

WAIT;

END PROCESS;

D_process: PROCESS

BEGIN

D <= '0';

WAIT FOR 40 ns;

D <= '1';

WAIT FOR 80 ns;

D <= '0';

WAIT FOR 20 ns;

D <= '1';

WAIT;

END PROCESS;

reset_PROCESS: PROCESS

BEGIN

reset <= '1';

WAIT FOR 10 ns;

reset <= '0';

WAIT FOR 30 ns;

reset <= '1';

WAIT FOR 10 ns;

reset <= '0';

WAIT FOR 30 ns;

reset <= '1';

WAIT;

END PROCESS;

enable_process: PROCESS

BEGIN

enable <= '0';

WAIT FOR 80 ns;

enable <= '1';

WAIT FOR 80 ns;

enable <= '0';

WAIT FOR 30 ns;

enable <= '1';

WAIT;

END PROCESS;

myclk_process: PROCESS

BEGIN

clk <= '0';

WAIT FOR 10 ns;

clk <= '1';

WAIT FOR 10 ns;

END PROCESS;

Q_process: PROCESS

BEGIN

Q <= '0';

WAIT FOR 20 ns;

Q <= '1';

WAIT FOR 20 ns;

Q <= '0';

WAIT FOR 20 ns;

Q <= '1';

WAIT FOR 20 ns;

Q <= '0';

WAIT;

END PROCESS;

--*************************************************************************************

-- SIMULATION CLK

--*************************************************************************************

simCLK_process: PROCESS

BEGIN

simCLK <= '0';

WAIT FOR 10 ns;

simCLK <= '1';

WAIT FOR 10 ns;

END PROCESS;

--*************************************************************************************

-- WRITE TEST CASE

--*************************************************************************************

write_TC_process: PROCESS

BEGIN

test_case <= '1';

write_tc <= PADDED_STRING("#TC-1", 32);

WAIT FOR 10 ns;

test_case <= '0';

WAIT FOR 60 ns;

test_case <= '1';

write_tc <= PADDED_STRING("#TC-2", 32);

WAIT FOR 10 ns;

test_case <= '0';

WAIT FOR 20 ns;

test_case <= '1';

write_tc <= PADDED_STRING("#TC-3", 32);

WAIT FOR 10 ns;

test_case <= '0';

WAIT FOR 40 ns;

test_case <= '1';

write_tc <= PADDED_STRING("#TC-4", 32);

WAIT FOR 10 ns;

test_case <= '0';

WAIT;

END PROCESS;

END RTL;