sakti_boy

Newbie level 4

Hallo,

I am quiet new with VHDL programming language.

Now, I make an FPGA as SPI Slave, and microcontroller as SPI Master.

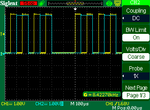

This Picture is the SPI Master from the microcontroller

(just normal SPI, without ChipSelect)

Yellow is the MOSI (0x55)

Blue is SCLK

FPGA receive the signal from SCLK and MOSI of microcontroller,

Here is my VHDL Program

-----------------------------------------------------------

-----------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_unsigned.all;

ENTITY spi_slave IS

GENERIC(

d_width : INTEGER := 8; --data bus width (8bit)

sclk1 : IN STD_LOGIC; --spi clk from master

mosi1 : IN STD_LOGIC; --master out, slave in

rx_data1 : OUT STD_LOGIC_VECTOR(d_width-1 DOWNTO 0);

END spi_slave;

ARCHITECTURE logic OF spi_slave IS

SIGNAL toggle : INTEGER RANGE 0 TO d_width := 0;

SIGNAL rx_buff1 : STD_LOGIC_VECTOR(d_width-1 DOWNTO 0) := (OTHERS => '0');

BEGIN

PROCESS(sclk1,toggle)

BEGIN

IF(rising_edge(sclk1)) THEN --rising edge, then capture the mosi

rx_buff1 <= rx_buff1(rx_buff1'left - 1 downto 0) & mosi1; -- capture mosi into rxbuff1

toggle <= toggle +1; --toggle as counter (8bit data received)

IF (toggle = 8) THEN --if toggle goes 8, then reset, and fill the output rx_data1 with rx_buff1

rx_data1 <= rx_buff1;

toggle <= 0;

END IF;

END IF;

END PROCESS;

END logic;

However, it did not really work.

Each output pin rx_data1, always goes high and low one after another, although I send always the same data 0x55

I think each pin will goes always low for the 0, and high for the 1, because the data is always the same.

The pin which should be 1 and 0, goes high and low in different phase ( I think, fpga can capture the spi master, there might be wrong with shifting)

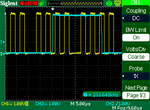

you can see picture here

it seems that every pins goes high and low, with next shifting measurement.

In this picture below,

yellow is mosi.

blue is one of output pin.

one of output (rx_data1) toggles on the next sequence of mosi input.

I have not implemented Chip Select, because my input pin of CS cannot detect the signal correctly,

but I think without CS, it will still work. (only one slave)

I have already spent several weeks, but it still the same. I am really stuck

Is there any one have this kind of experience before ?

or Maybe anyone know what is wrong with my program ?

Any helps, suggestions will be very appreciated.

Thanks in advance

I am quiet new with VHDL programming language.

Now, I make an FPGA as SPI Slave, and microcontroller as SPI Master.

This Picture is the SPI Master from the microcontroller

(just normal SPI, without ChipSelect)

Yellow is the MOSI (0x55)

Blue is SCLK

FPGA receive the signal from SCLK and MOSI of microcontroller,

Here is my VHDL Program

-----------------------------------------------------------

-----------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_unsigned.all;

ENTITY spi_slave IS

GENERIC(

d_width : INTEGER := 8; --data bus width (8bit)

sclk1 : IN STD_LOGIC; --spi clk from master

mosi1 : IN STD_LOGIC; --master out, slave in

rx_data1 : OUT STD_LOGIC_VECTOR(d_width-1 DOWNTO 0);

END spi_slave;

ARCHITECTURE logic OF spi_slave IS

SIGNAL toggle : INTEGER RANGE 0 TO d_width := 0;

SIGNAL rx_buff1 : STD_LOGIC_VECTOR(d_width-1 DOWNTO 0) := (OTHERS => '0');

BEGIN

PROCESS(sclk1,toggle)

BEGIN

IF(rising_edge(sclk1)) THEN --rising edge, then capture the mosi

rx_buff1 <= rx_buff1(rx_buff1'left - 1 downto 0) & mosi1; -- capture mosi into rxbuff1

toggle <= toggle +1; --toggle as counter (8bit data received)

IF (toggle = 8) THEN --if toggle goes 8, then reset, and fill the output rx_data1 with rx_buff1

rx_data1 <= rx_buff1;

toggle <= 0;

END IF;

END IF;

END PROCESS;

END logic;

However, it did not really work.

Each output pin rx_data1, always goes high and low one after another, although I send always the same data 0x55

I think each pin will goes always low for the 0, and high for the 1, because the data is always the same.

The pin which should be 1 and 0, goes high and low in different phase ( I think, fpga can capture the spi master, there might be wrong with shifting)

you can see picture here

it seems that every pins goes high and low, with next shifting measurement.

In this picture below,

yellow is mosi.

blue is one of output pin.

one of output (rx_data1) toggles on the next sequence of mosi input.

I have not implemented Chip Select, because my input pin of CS cannot detect the signal correctly,

but I think without CS, it will still work. (only one slave)

I have already spent several weeks, but it still the same. I am really stuck

Is there any one have this kind of experience before ?

or Maybe anyone know what is wrong with my program ?

Any helps, suggestions will be very appreciated.

Thanks in advance