luoyanghero

Junior Member level 3

- Joined

- Nov 22, 2016

- Messages

- 29

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- ShengXiaLu

- Activity points

- 1,219

//This is the verilog standard document discription:

//The seed argument controls the numbers that $random returns so that different seeds generate different random streams. The seed argument shall be an integral variable. The seed value should be assigned to this variable prior to calling $random.

//I did a test.

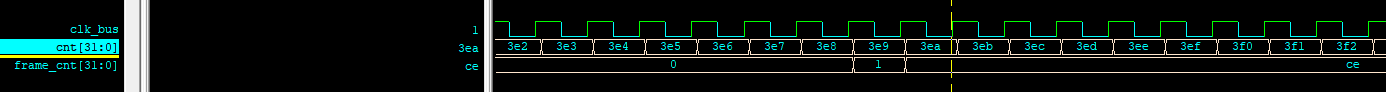

//frame_cnt be force changed from 32'h1 to 32'hce.

//The seed argument controls the numbers that $random returns so that different seeds generate different random streams. The seed argument shall be an integral variable. The seed value should be assigned to this variable prior to calling $random.

//I did a test.

C:

`ifndef DLY

`define DLY 1

`endif

module tb_top;

reg clk_bus;

reg brst_n;

reg [31:0] frame_cnt;

reg [31:0] cnt;

initial begin

brst_n = 1'b1;

#1;

brst_n = 1'b0;

#100;

brst_n = 1'b1;

#1000000000;

//$finish;

end

initial begin

clk_bus = 1'b0;

forever #5 clk_bus = ~clk_bus;

end

always @ (posedge clk_bus or negedge brst_n) begin

if (~brst_n)

cnt[31:0] <= #`DLY 'd0;

else

cnt[31:0] <= #`DLY cnt + 1;

end

always @ (posedge clk_bus or negedge brst_n) begin

if (~brst_n)

frame_cnt[31:0] <= #`DLY 32'd0;

else if (cnt==1000)

frame_cnt[31:0] <= #`DLY frame_cnt + 1;

end

integer end_dly;

initial begin

end_dly = 1;

while (1) begin

@(posedge clk_bus);

if (cnt==1001) begin

#`DLY end_dly = $random(frame_cnt[7:0]);//luoy why random seed(frame_cnt[7:0]) be force changed?

end

end

end

initial begin

//wait ((in_data_drv.frm_cnt == 1) && (in_data_drv.mb_y_cnt == 90));

$fsdbDumpfile("tb_top.fsdb");

$fsdbDumpvars(tb_top, 0);

end

endmodule//frame_cnt be force changed from 32'h1 to 32'hce.