vlsiexpert

Newbie

Need help on a simple system verilog code

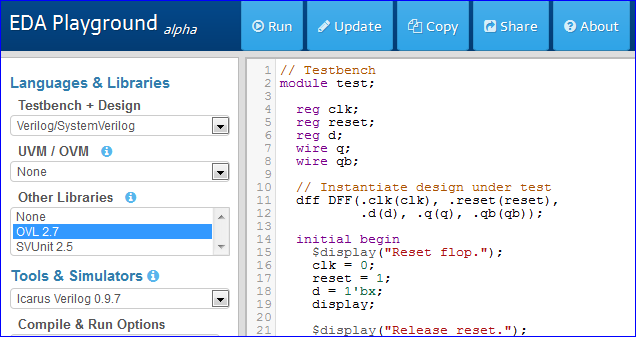

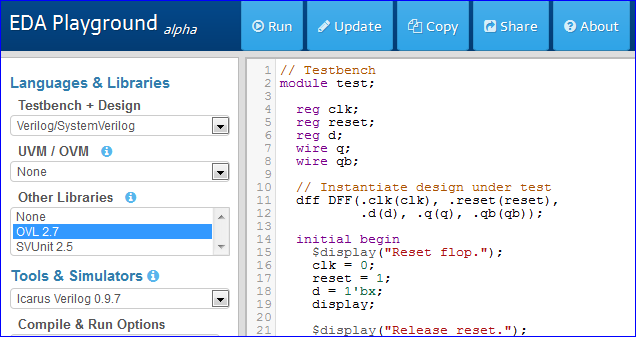

www.edaplayground.com

www.edaplayground.com

1. class packet has dynamic array data[] and it's size is constrained between 1 to 250

2. Extending the packet class to small_packet and constraining size to be less than 10

3. casting small_packet to packet class's object

I would expect the size should be always less than 10, but it is not obeying the constraint in extended class

Any help?code link

[ MODERATOR ACTION ] Upload original code here

EDA Playground

Edit, save, simulate, synthesize SystemVerilog, Verilog, VHDL and other HDLs from your web browser.

1. class packet has dynamic array data[] and it's size is constrained between 1 to 250

2. Extending the packet class to small_packet and constraining size to be less than 10

3. casting small_packet to packet class's object

I would expect the size should be always less than 10, but it is not obeying the constraint in extended class

Any help?code link

[ MODERATOR ACTION ] Upload original code here

Code Verilog - [expand]

Last edited by a moderator: