mohazaga

Full Member level 2

Hi,,,

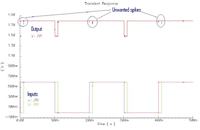

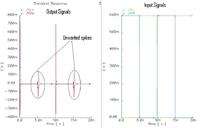

I hope every body is ok , i have problem of design ckt , well I apply two inverted signal pulse (one delayed to other) to NAND gate .In the result there is some unwanted spikes since the output should be 0 as both signals are 1 (this is ok) but in other cases there are spike ? Why ? how to solve?

thanks

I hope every body is ok , i have problem of design ckt , well I apply two inverted signal pulse (one delayed to other) to NAND gate .In the result there is some unwanted spikes since the output should be 0 as both signals are 1 (this is ok) but in other cases there are spike ? Why ? how to solve?

thanks