yefj

Advanced Member level 4

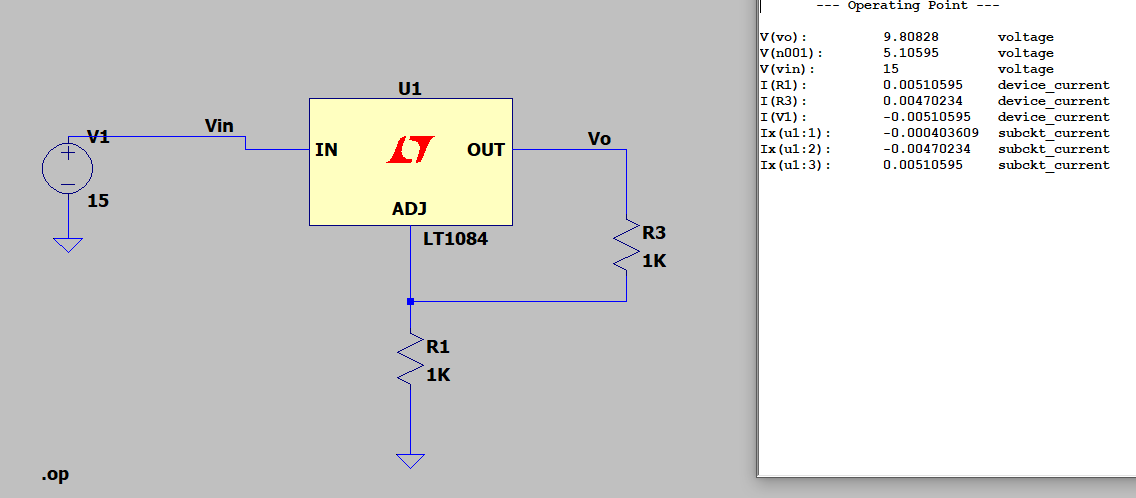

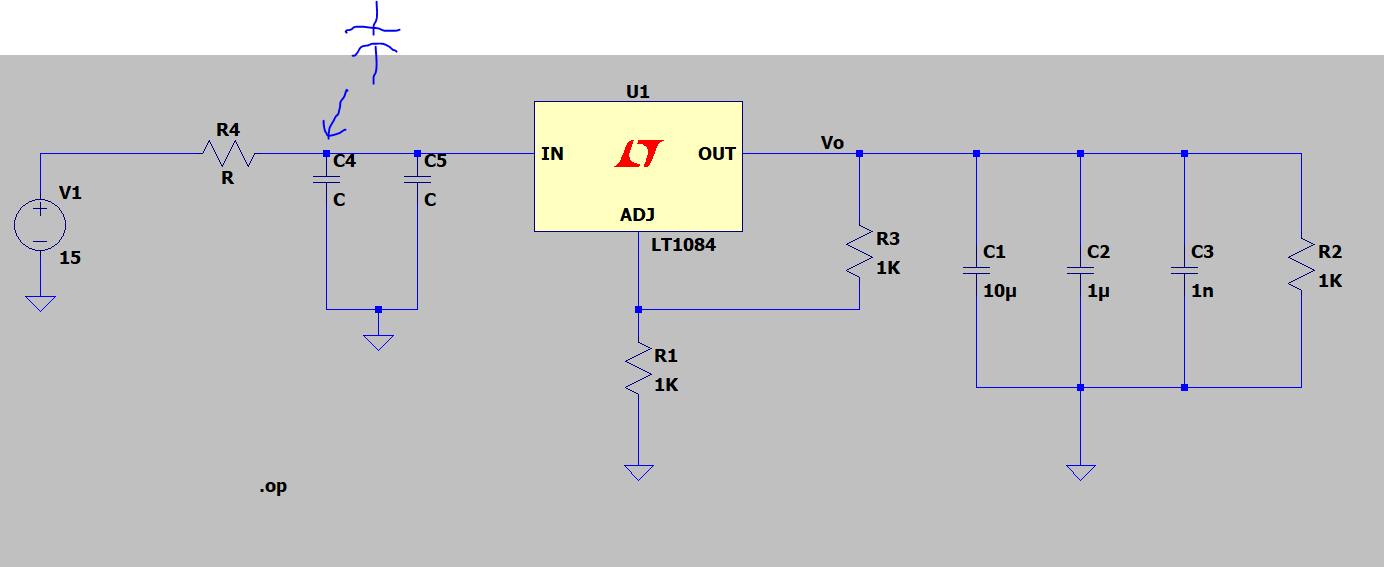

Hello, I have a basic regulator shown below. I use LT1084 instead of LD1084 and As you can see the simulator works great without capacitors.

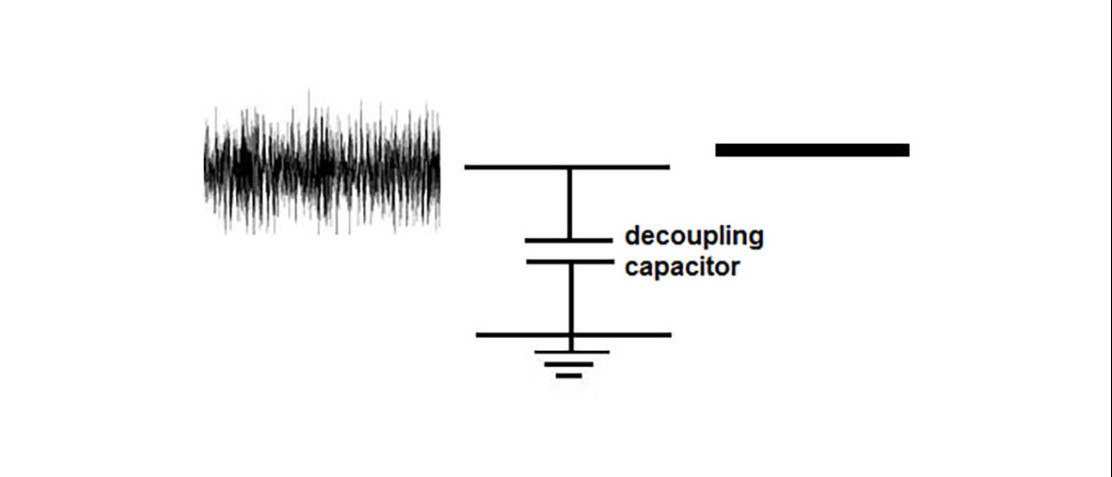

I understand that capacitors are used to filter out the noise from power supply.

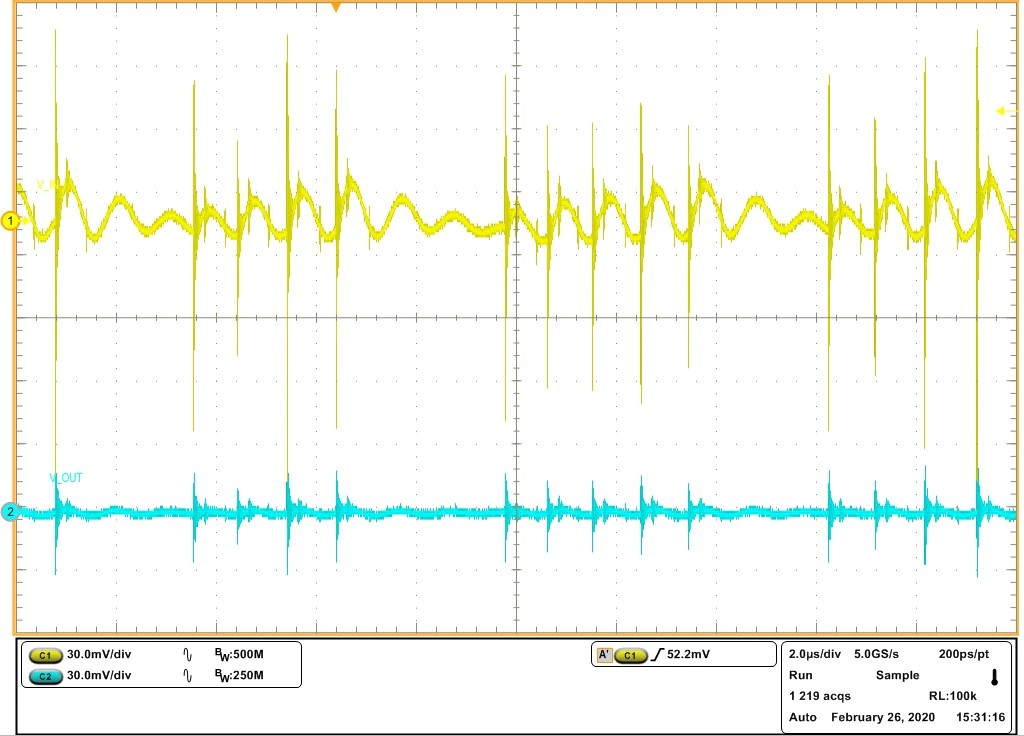

I have a circuit which uses a lot of capacitors both near input and output as shown in the photo in the end.

1.The network starts with polarised capacitor as shown in the blue arrow, why polarized?

2.why we have two networks both input and ouput?

3.I know how to simulation AC filter responce. how can i know based on the networks to what purpose they where planned for?

Thanks.

LD1084:

LT1084:

I understand that capacitors are used to filter out the noise from power supply.

I have a circuit which uses a lot of capacitors both near input and output as shown in the photo in the end.

1.The network starts with polarised capacitor as shown in the blue arrow, why polarized?

2.why we have two networks both input and ouput?

3.I know how to simulation AC filter responce. how can i know based on the networks to what purpose they where planned for?

Thanks.

LD1084:

LD1084V pdf, LD1084V Description, LD1084V Datasheet, LD1084V view ::: ALLDATASHEET :::

LD1084V Datasheet, LD1084V datasheets, LD1084V pdf, LD1084V integrated circuits : STMICROELECTRONICS - 5A LOW DROP POSITIVE VOLTAGE REGULATOR ADJUSTABLE AND FIXED ,alldatasheet, Datasheet, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes, triacs and...

pdf1.alldatasheet.com

LT1084:

LT1084 pdf, LT1084 Description, LT1084 Datasheet, LT1084 view ::: ALLDATASHEET :::

LT1084 Datasheet, LT1084 datasheets, LT1084 pdf, LT1084 integrated circuits : LINER - 3A, 5A, 7.5A Low Dropout Positive Fixed Regulators ,alldatasheet, Datasheet, Datasheet search site for Electronic Components and Semiconductors, integrated circuits, diodes, triacs and other semiconductors.

pdf1.alldatasheet.com