yschuang

Full Member level 3

Hello, all

I am reading an application note as follows.

www.intersil.com/data/an/an051.pdf

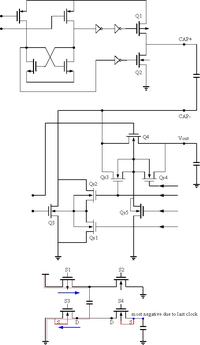

1. I was wondering how to turn off Q3 and Q4 with a voltage level translator.

Q3 or Q4 is turned off if Vgs,q3<Vt, which implies Vg,q3-Vs,q3<Vt. Vg,q3<Vt+Vs,q3. Vs,q3 is negatvie as I know. Therefore, Vg,q3 has to be

negative, too. Is that right and possible and how to implement that with a

voltage level translator ?

2. Am I right about drains and sources in each time ?

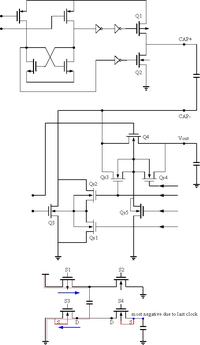

Fig. S1 represents one clock when S1 and S3 are on.

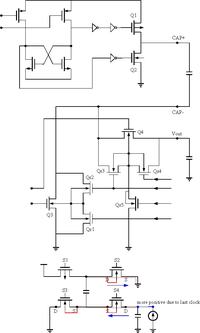

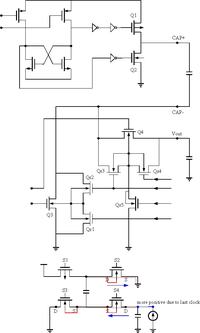

Fig. S2 represents another clock when S2 and S4 are on.

Drains and sources of Q3 and Q4 are on each figure and important because Q3 and Q4 require drive considerations like the application note said. Drains and sources are inverted each time. This is why i try to mark drains and sources in each time.

3. What is Qs5 for ?

Thanks

I am reading an application note as follows.

www.intersil.com/data/an/an051.pdf

1. I was wondering how to turn off Q3 and Q4 with a voltage level translator.

Q3 or Q4 is turned off if Vgs,q3<Vt, which implies Vg,q3-Vs,q3<Vt. Vg,q3<Vt+Vs,q3. Vs,q3 is negatvie as I know. Therefore, Vg,q3 has to be

negative, too. Is that right and possible and how to implement that with a

voltage level translator ?

2. Am I right about drains and sources in each time ?

Fig. S1 represents one clock when S1 and S3 are on.

Fig. S2 represents another clock when S2 and S4 are on.

Drains and sources of Q3 and Q4 are on each figure and important because Q3 and Q4 require drive considerations like the application note said. Drains and sources are inverted each time. This is why i try to mark drains and sources in each time.

3. What is Qs5 for ?

Thanks