yefj

Advanced Member level 4

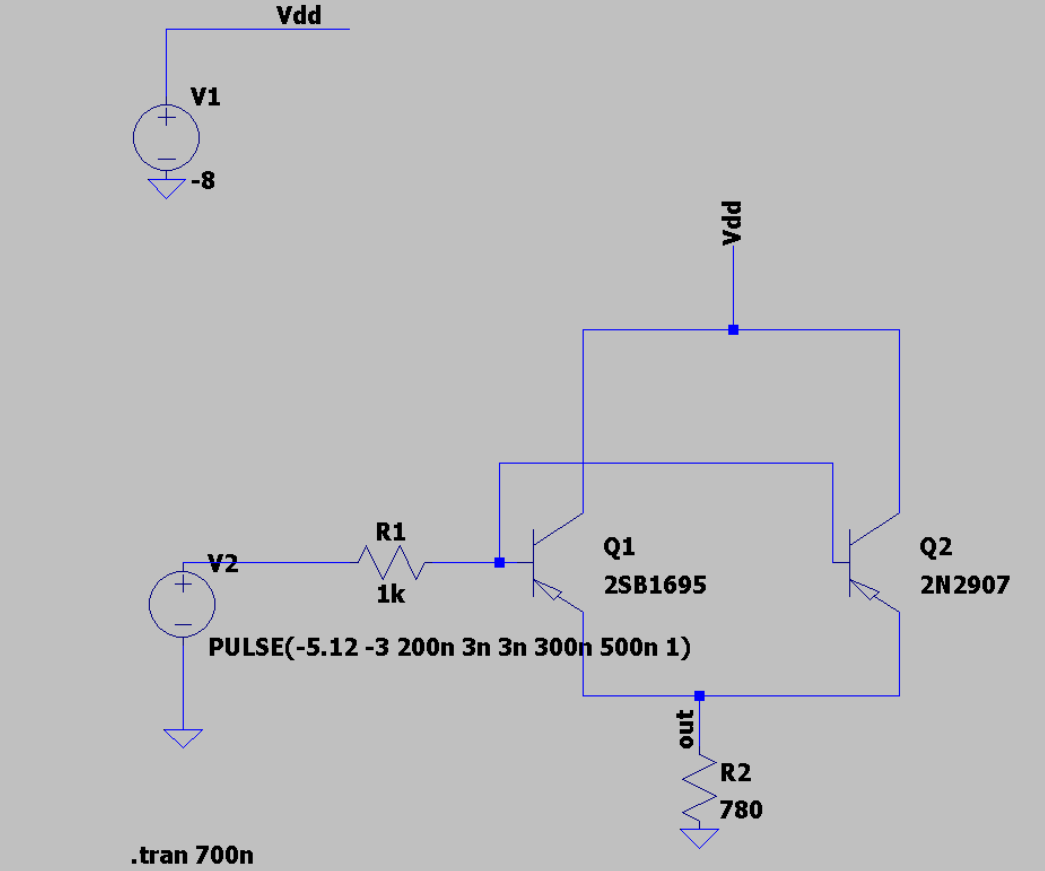

Hello,I have the following circuit where my output is on the buttom call out net.

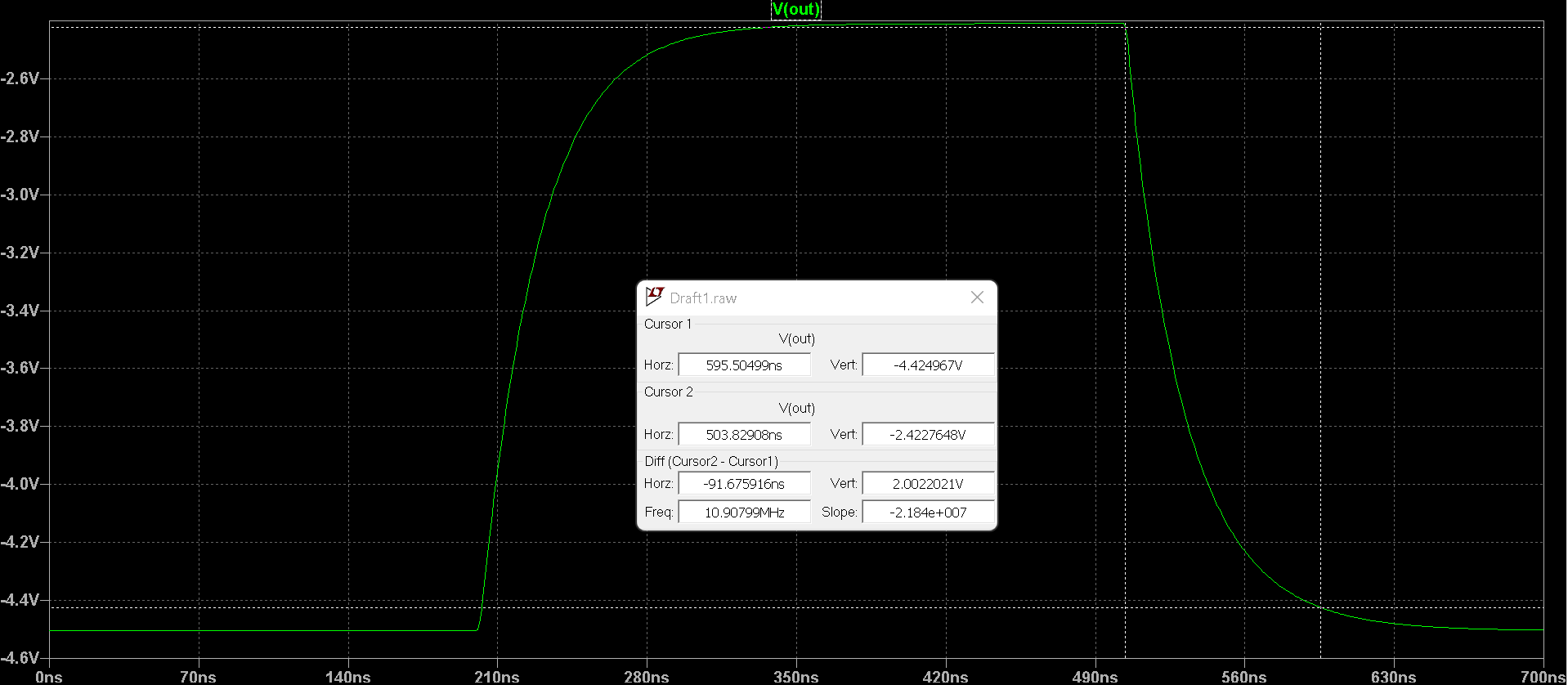

as you can see my out pulse has a very big charge and discharge time.

Is there a way to make the out pulse charge and discharge faster?

Thanks.

as you can see my out pulse has a very big charge and discharge time.

Is there a way to make the out pulse charge and discharge faster?

Thanks.