newbie_hs

Full Member level 1

Dear Team,

This is a continuation of this question.

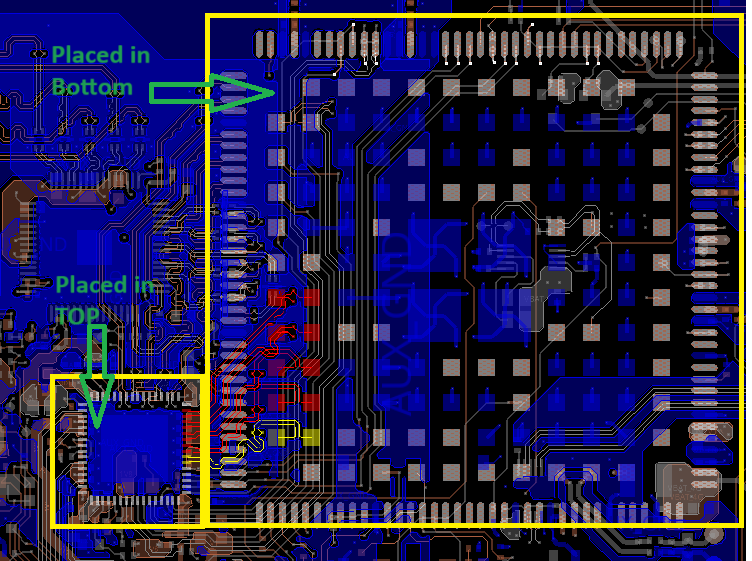

In my board DS90UB960 is placed in top and SC206E is placed in bottom.

Please see the below image

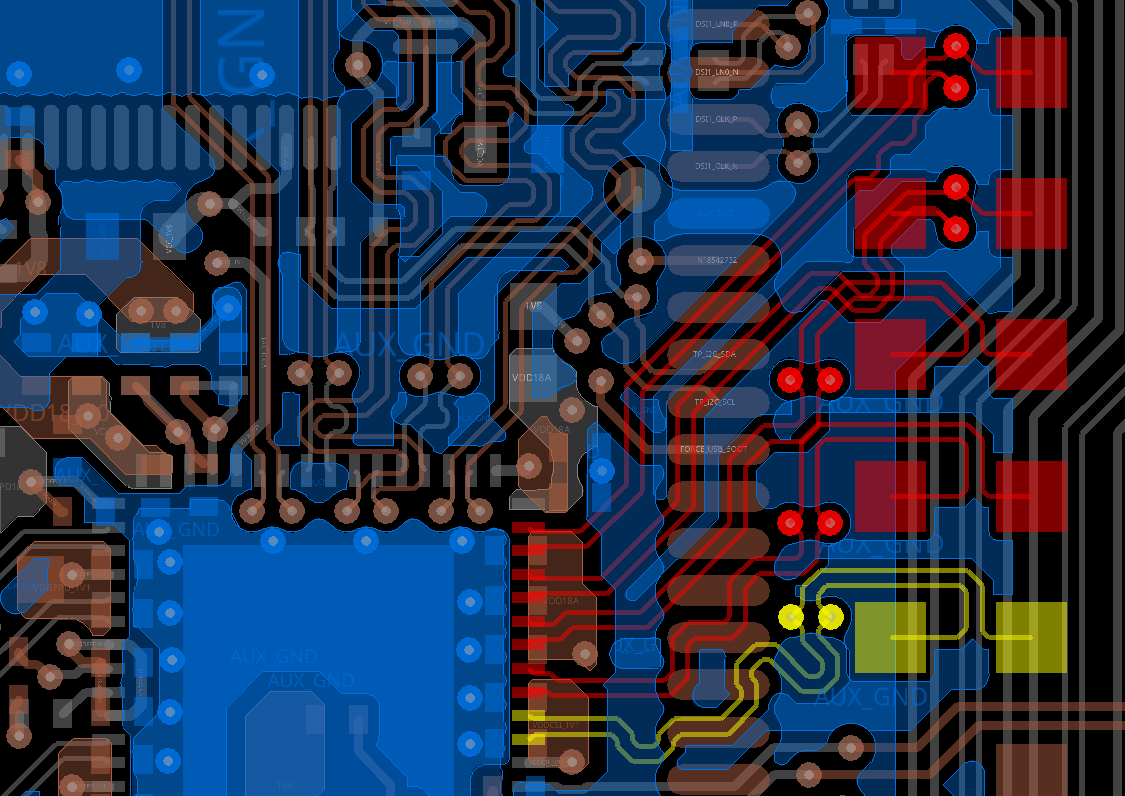

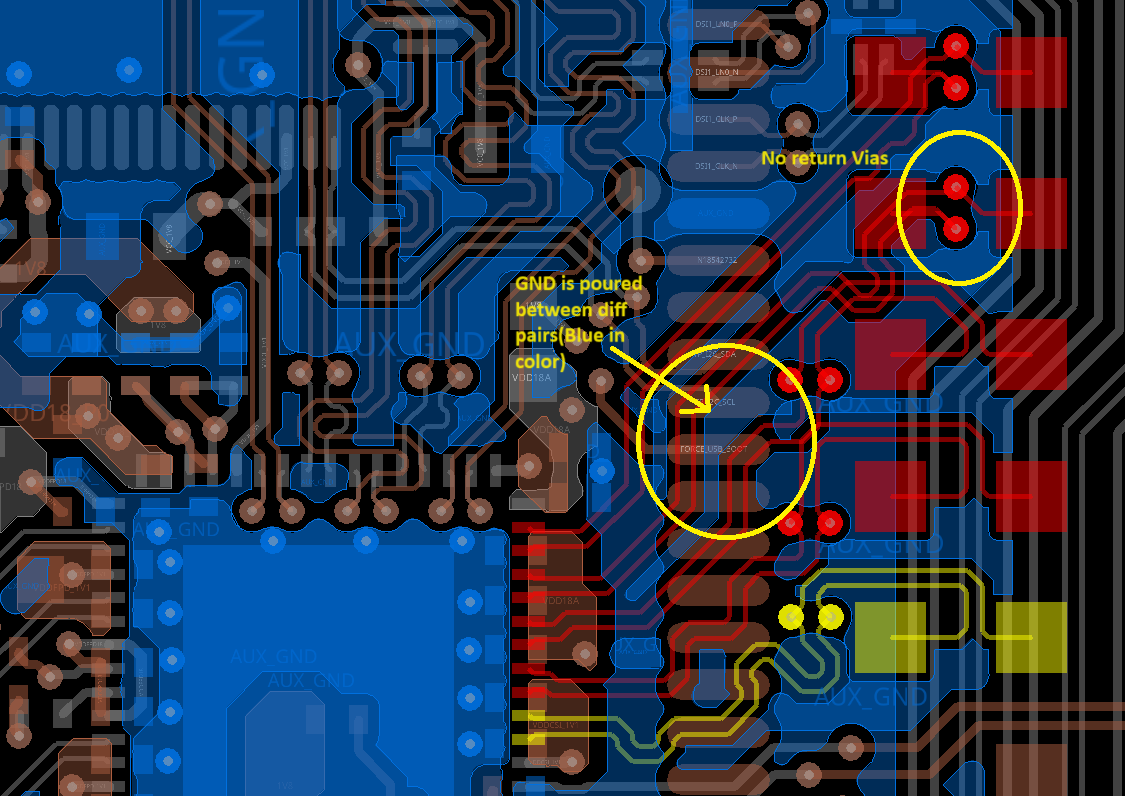

Below is the enlarged version of CSI0 interface. The yellow color signals are clock and red color are CSI0 t0 3 data line.

These signals are travelling from top to bottom. But there is no return vias are provided.What you see in blue color is the ground

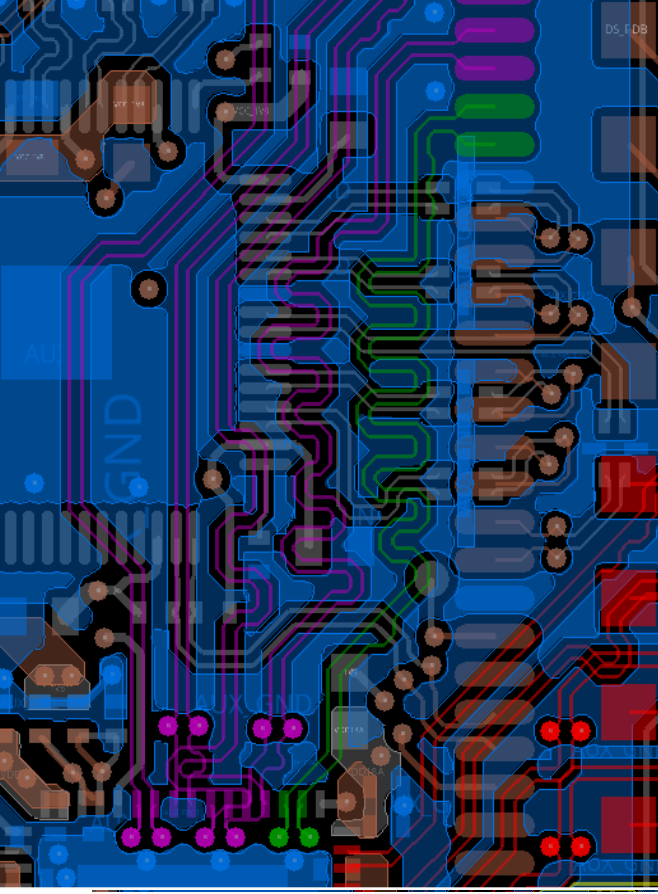

Below is the CSI1 signals. Green is the clock

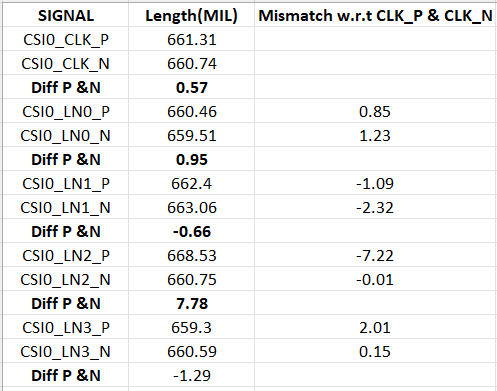

Trace length details are given below.

This is a continuation of this question.

In my board DS90UB960 is placed in top and SC206E is placed in bottom.

Please see the below image

Below is the enlarged version of CSI0 interface. The yellow color signals are clock and red color are CSI0 t0 3 data line.

These signals are travelling from top to bottom. But there is no return vias are provided.What you see in blue color is the ground

- My question is do we need to place return vias near symmetrical to the vias which are moving from top to bottom.

- Is it a good idea to pour GND in between differential pairs.You can see that in between CSIO_D1 and CSI0_D2 gnd is poured.As per my knowledge this will affect the impedance of the trace.Please correct me if I am wrong

Below is the CSI1 signals. Green is the clock

Trace length details are given below.

Last edited: