Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 262

Hi, I am tring to simulate a design, but i found some different result. I dotn know why?

Here is a simple.

Verilog code:

TestBench in iVerilog:

TestBench in VCS:

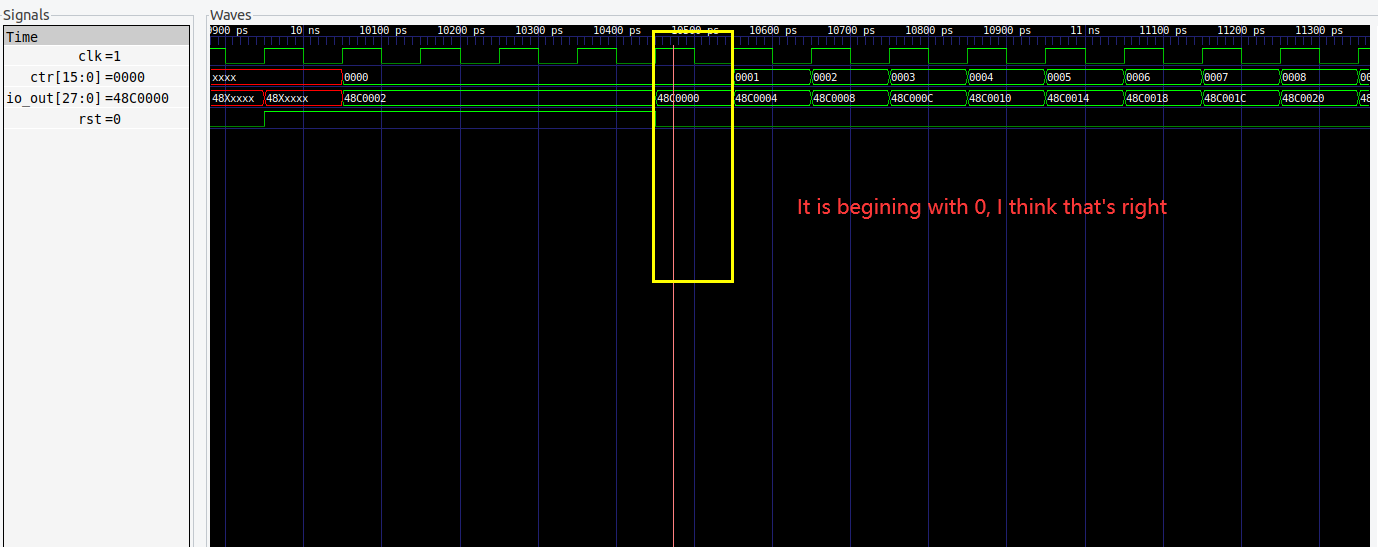

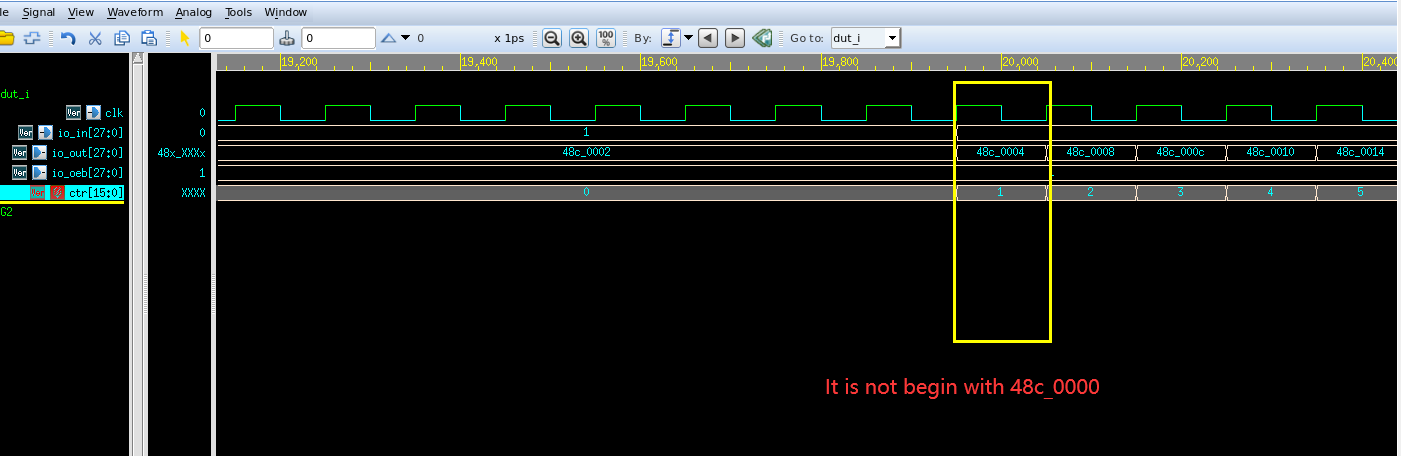

Result: ( it is different between this two tools, VCS dont begin as it should be)

iVerilog:

VCS:

Here is a simple.

Verilog code:

Code:

module top(input wire clk, input wire [27:0] io_in, output wire [27:0] io_out, io_oeb);

wire rst = io_in[0];

reg [15:0] ctr;

always @(posedge clk)

if (rst)

ctr <= 0;

else

ctr <= ctr + 1'b1;

assign io_out = {10'h123, ctr, rst, 1'b0}; // pass thru reset for debugging

assign io_oeb = 28'b1;

endmodule

Code:

`timescale 1ps/1ps

module fab_tb;

wire [27:0] I_top;

wire [27:0] T_top;

reg [27:0] O_top = 0;

reg CLK = 1'b0;

wire [27:0] I_top_gold, oeb_gold, T_top_gold;

top dut_i (

.clk(CLK),

.io_out(I_top_gold),

.io_oeb(oeb_gold),

.io_in(O_top)

);

assign T_top_gold = ~oeb_gold;

always #50 CLK = (CLK === 1'b0);

integer i;

reg have_errors = 1'b0;

initial begin

repeat (100) @(posedge CLK);

O_top = 28'b1; // reset

repeat (5) @(posedge CLK);

O_top = 28'b0;

for (i = 0; i < 100; i = i + 1) begin

@(negedge CLK);

$display("cnt = 0x%X, f gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

if (I_top !== I_top_gold)

have_errors = 1'b1;

if (T_top !== T_top_gold)

have_errors = 1'b1;

end

if (have_errors)

$fatal;

else

$finish;

end

initial begin

$dumpfile("wave.vcd"); //

$dumpvars(0, fab_tb);

end

endmodule

module clk_buf(input A, output X);

assign X = A;

endmodule

Code:

`timescale 1ps/1ps

module adder_tb;

reg [27:0] O_top = 0;

reg CLK = 1'b1;

wire [27:0] I_top_gold, oeb_gold, T_top_gold;

top dut_i (

.clk(CLK),

.io_out(I_top_gold),

.io_oeb(oeb_gold),

.io_in(O_top)

);

assign T_top_gold = ~oeb_gold;

always #50 CLK = (CLK === 1'b0);

//always begin

//#50

//CLK = ~CLK;

//end

//always #50 CLK = ~CLK ;

integer i;

reg have_errors = 1'b0;

initial begin

CLK = 0;

repeat (100) @(posedge CLK);

O_top = 28'b1; // reset

repeat (100) @(posedge CLK);

O_top = 28'b0;

//repeat (50) @(posedge CLK);

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", O_top, I_top_gold, T_top_gold);

for (i = 0; i < 100; i = i + 1) begin

@(negedge CLK);

$display("in_in = 0x%X, gold = 0x%X, gold = 0x%X", CLK, I_top_gold, T_top_gold);

end

if (have_errors)

$fatal;

else

$finish;

end

initial begin

$fsdbDumpfile("adder_tb.fsdb"); //

$fsdbDumpvars(0,adder_tb); //

$fsdbDumpSVA();

$fsdbDumpMDA();

$vcdpluson;

$vcdplusmemon;

end

endmodule

module clk_buf(input A, output X);

assign X = A;

endmoduleResult: ( it is different between this two tools, VCS dont begin as it should be)

iVerilog:

VCS: