rastor

Newbie level 6

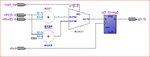

I have the following code:

my question is how can i connect q to one of the input of the bottom adder. i tried

but no luck. Any idea/suggestions? I have attached the output image of the above code.

Thank you.

Code:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

Entity count1s IS

PORT ( oPC : in std_logic_vector(3 downto 0);

offset: in std_logic_vector(3 downto 0);

load_bta : in std_logic;

q : out std_logic_vector(3 downto 0);

clock : in std_logic );

end count1s;

architecture arch of count1s is

SIGNAL c1 : std_logic_vector(3 downto 0);

SIGNAL c2 : std_logic_vector(3 downto 0);

begin

process(clock)

begin

c1 <= oPC + "0001";

c2 <= oPC + offset;

if (clock'event and clock='1') then

if (load_bta='1') then

q<=c1;

else

q<=c2;

end if;

end if;

end process;

end arch;my question is how can i connect q to one of the input of the bottom adder. i tried

Code:

oPC <= q;Thank you.