RadioHobbies

Newbie level 4

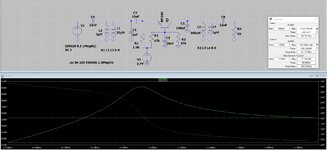

Trying to adjust the bias of the above circuit , I noticed that the 37 k pot need to be at its highest value ,

ie : the circuit need more positive voltage on the base

then the maximum gain I've got was when I connect the base to the ground (positive terminal by removing resistors & cap)

That gain wasn't enough though

I thought of the collector should have a resistor to make the pot have a center point

I added a 2.7 k resistor to the circuit in the series with the collector (and a 103 cap for passing the signal to the ground), that was right ,

the pot now have a center point where the gain reach its maximum value ,

then get decreased when the pot value exceed some point but in that arrangement , the gain became

very low (less than before)

I am not familiar with common base amplifiers

any suggestions please ?