ustinoff

Member level 2

Hello. I do not understand, how i can do next thing.

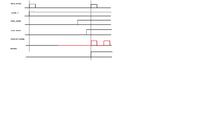

I want to get "clock_out" with the same frequancy that "slow_clock", but

if "enable" changing from '0' to '1' or after 1-3 times of "fast_clock"

my next blocks must feel changing from low front to high front (rising_edge(clk) in terms of VHDL).

I tried to do it with next code:

I want to get "clock_out" with the same frequancy that "slow_clock", but

if "enable" changing from '0' to '1' or after 1-3 times of "fast_clock"

my next blocks must feel changing from low front to high front (rising_edge(clk) in terms of VHDL).

I tried to do it with next code:

Code:

process(enb,fast_clock,slow_clock)

begin

if rising_edge(fast_clock) then

if enb='1' then

if slow_clock='1' then

clock_out <= slow_clock;

elsif slow_clock='0' then

clk_out <= not(slow_clock);

end if;

else

clk_out <= '0';

end if;

end if;

end process;