Prashanthanilm

Full Member level 5

- Joined

- Aug 24, 2012

- Messages

- 302

- Helped

- 36

- Reputation

- 72

- Reaction score

- 36

- Trophy points

- 1,308

- Activity points

- 2,950

Hi,

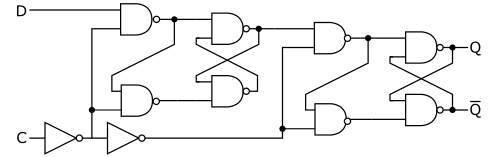

What is the need of transmission gate in FF?

I mean rather than clock signal (transparent and non-transparent).

What if I don't put TG in my feedback circuit. How it will effect my schematics performance?

Thank you,

Prashanth

What is the need of transmission gate in FF?

I mean rather than clock signal (transparent and non-transparent).

What if I don't put TG in my feedback circuit. How it will effect my schematics performance?

Thank you,

Prashanth