Osawa_Odessa

Banned

Hi,

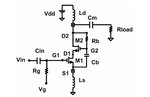

I want to analyse the circuit below. It is an RF power amplifier.

In DC mode:

Assuming that Ld is ideal then there is no DC voltage drop across it. => VD2 = VDD.

In the mean time, the capacitor is open at DC => no current flowing through Rb => VG2 = VD2 = VDD

In AC mode:

This is where I am confused. It is said that M2 acts as common gate here. This means that the gate of M2, G2, have to be connected to ground in AC mode, right?

But how can that be possible when there is the presence of Cb and Ls?

The voltage at gate of M2, VG2, will be equal to the total voltage across Cb and Ls. But VG2 is impossible zero, right?

And if so how M2 can be a common gate stage? Please explain? Thanks.

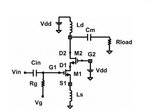

I want to analyse the circuit below. It is an RF power amplifier.

In DC mode:

Assuming that Ld is ideal then there is no DC voltage drop across it. => VD2 = VDD.

In the mean time, the capacitor is open at DC => no current flowing through Rb => VG2 = VD2 = VDD

In AC mode:

This is where I am confused. It is said that M2 acts as common gate here. This means that the gate of M2, G2, have to be connected to ground in AC mode, right?

But how can that be possible when there is the presence of Cb and Ls?

The voltage at gate of M2, VG2, will be equal to the total voltage across Cb and Ls. But VG2 is impossible zero, right?

And if so how M2 can be a common gate stage? Please explain? Thanks.