godsun

Junior Member level 3

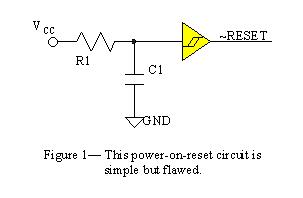

i know that most power on reset circuit is RC+Schmitt-trigger

but assume RC delay is 1s, Vcc stable is 10s, but one glitch happened and it is 100ms

then it is not long enough for RC discharge ,which will result in reset not active and meta state of system .

how to avoid it? only choice RC according to system?

but assume RC delay is 1s, Vcc stable is 10s, but one glitch happened and it is 100ms

then it is not long enough for RC discharge ,which will result in reset not active and meta state of system .

how to avoid it? only choice RC according to system?