cupoftea

Advanced Member level 5

Hi,

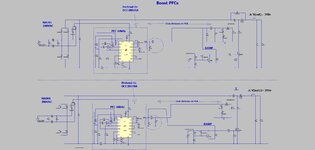

Which of the Boost PFC schems is best? One has the current sense resistor near the controller, and the other has the current sense resistor near the current sense transformer output. There is a decent ground plane under all of it.

Which is best, top or bottom schem?

LTspice sim and jpeg schem attached.

UCC28070A PFC controller datasheet

Which of the Boost PFC schems is best? One has the current sense resistor near the controller, and the other has the current sense resistor near the current sense transformer output. There is a decent ground plane under all of it.

Which is best, top or bottom schem?

LTspice sim and jpeg schem attached.

UCC28070A PFC controller datasheet