nikhillife11

Member level 2

Hey All,

I need your help. I am currently working on LPC2148 and trying to write my program for LCD. I googled some pages and came accros a common function for initializing PLL of LPC2148

But my question is.... If i am using a 12 MHZ crystal at the xtal1 and xtal2 pin of LPC2148,what will the CPU clock be and Peripheral clock be from below function

void clkinit(void)

{

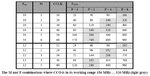

PLL0CFG=0x24;

PLL0FEED=0xAA;

PLL0FEED=0x55;

PLL0CON=0x01;

PLL0FEED=0xAA;

PLL0FEED=0x55;

while(!(PLL0STAT & PLOCK));

PLL0CON=0x03;

PLL0FEED=0xAA;

PLL0FEED=0x55;

MAMCR=0x02; // why this initialization

MAMTIM=0x04; // Again why this one

VPBDIV=0x01;

}

I need to know my CPU and Peripheral clock to calculate the approx. delay.

So pl. help me out friends

thanks

Nikhil

I need your help. I am currently working on LPC2148 and trying to write my program for LCD. I googled some pages and came accros a common function for initializing PLL of LPC2148

But my question is.... If i am using a 12 MHZ crystal at the xtal1 and xtal2 pin of LPC2148,what will the CPU clock be and Peripheral clock be from below function

void clkinit(void)

{

PLL0CFG=0x24;

PLL0FEED=0xAA;

PLL0FEED=0x55;

PLL0CON=0x01;

PLL0FEED=0xAA;

PLL0FEED=0x55;

while(!(PLL0STAT & PLOCK));

PLL0CON=0x03;

PLL0FEED=0xAA;

PLL0FEED=0x55;

MAMCR=0x02; // why this initialization

MAMTIM=0x04; // Again why this one

VPBDIV=0x01;

}

I need to know my CPU and Peripheral clock to calculate the approx. delay.

So pl. help me out friends

thanks

Nikhil