pacman22

Junior Member level 1

Hey!

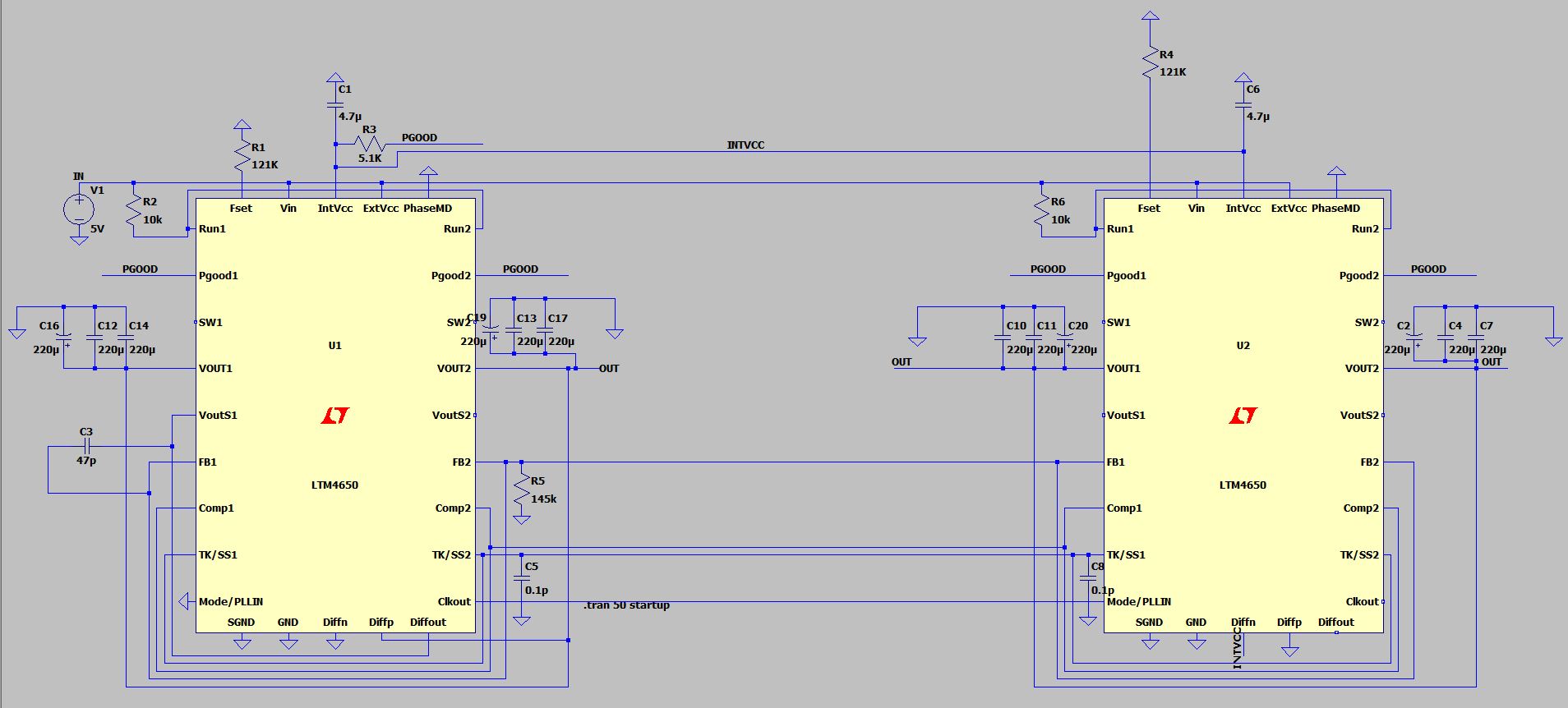

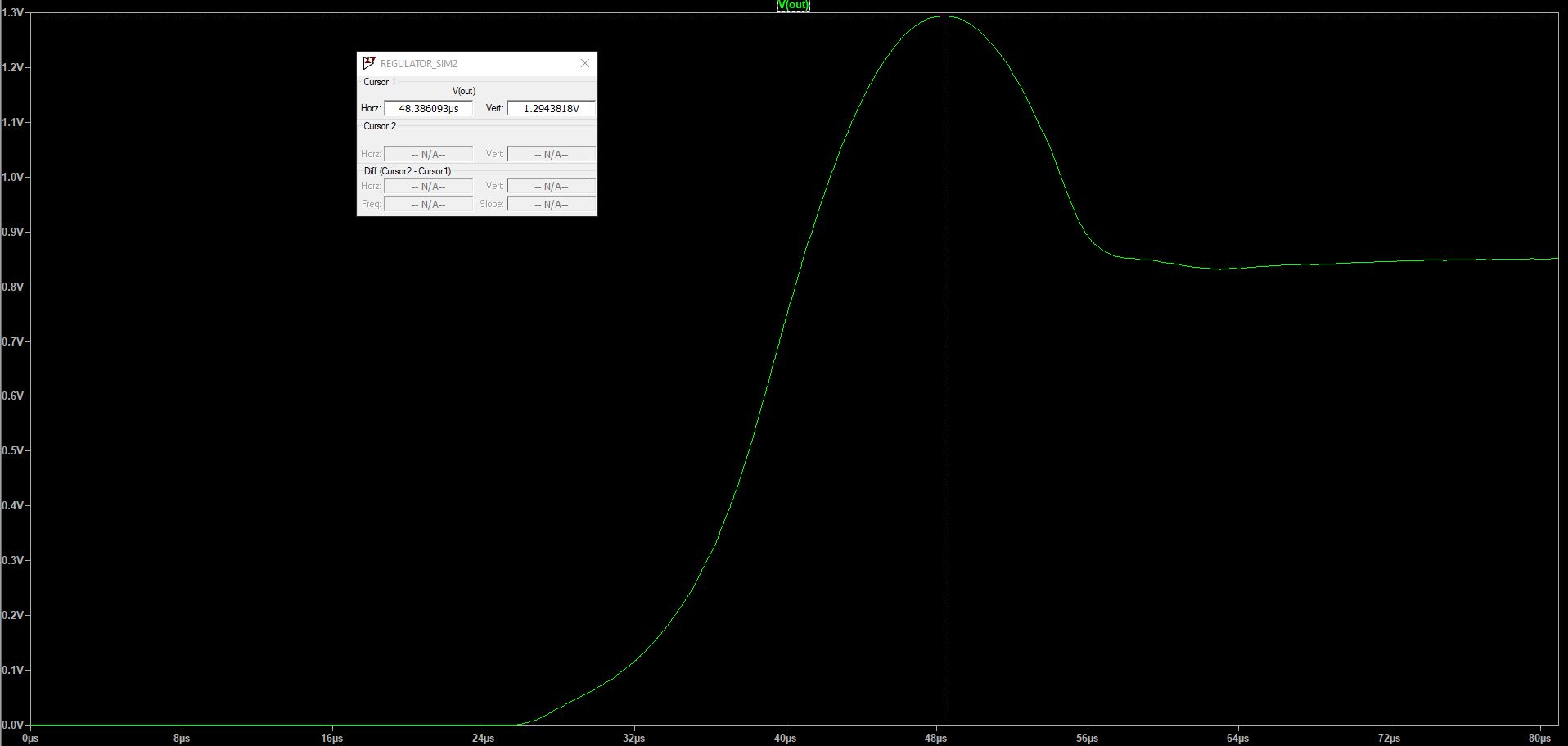

I have designed a 4 phase regulator to output 0.85V @100A using LTM4650 and simulated it on LTSpice. During transient analysis, I found that there is a voltage spike till 1.29V and then stabilizes to 0.85V.

This spike can not be tolerated for SoC application. Can you suggest how this spike can be eliminated?

I have designed a 4 phase regulator to output 0.85V @100A using LTM4650 and simulated it on LTSpice. During transient analysis, I found that there is a voltage spike till 1.29V and then stabilizes to 0.85V.

This spike can not be tolerated for SoC application. Can you suggest how this spike can be eliminated?