krisdan

Banned

- Joined

- Oct 17, 2014

- Messages

- 4

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 0

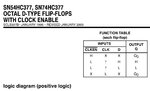

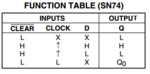

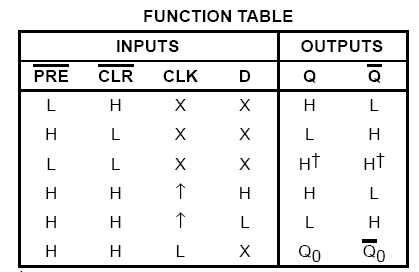

good *** gurus in the house... can anyone help me with the vhdl code for an octal d-type flip flops with clock enable? thanks waiting for your urgent replies....