sumozgdyrqicsyhcnn

Newbie

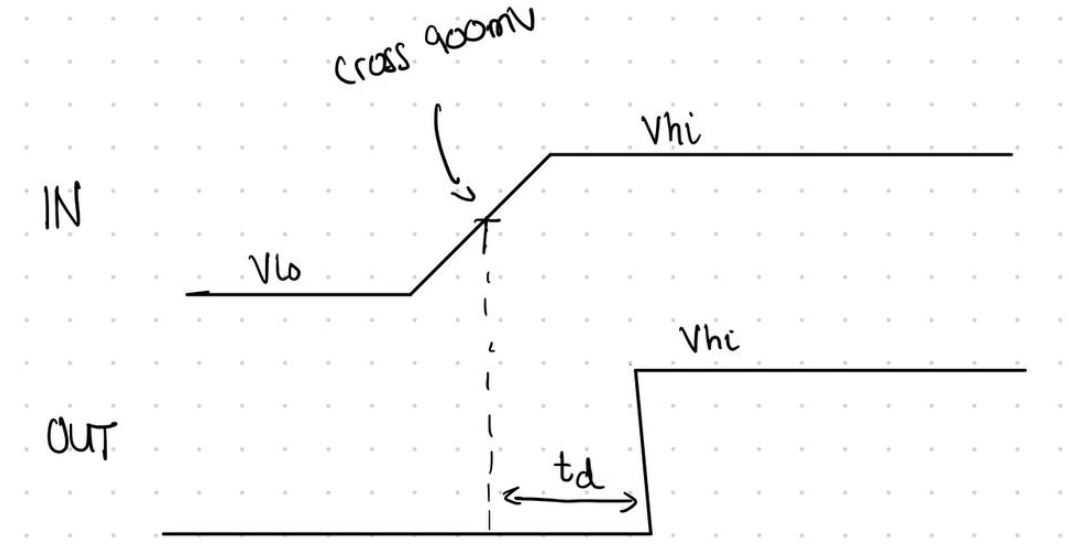

Desired Behaviour:

Code:

I keep getting an error saying that the transition operator cannot be used nested in a conditional. How else am I supposed to cause a transition at particular point in time???

Code:

Code:

module clk_gen(in, out)

input in;

output out;

electrical in, out;

parameter td = 100n;

real rise_abstime;

analog begin

@(cross(V(in) - 900m, +1)) begin

rise_abstime = $abstime;

end

@(timer(rise_abstime+td)) begin

V(out) <+ transition(0, 1.8, 1n)

end

endI keep getting an error saying that the transition operator cannot be used nested in a conditional. How else am I supposed to cause a transition at particular point in time???