stark43

Member level 1

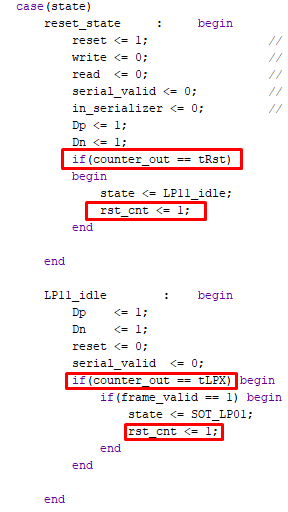

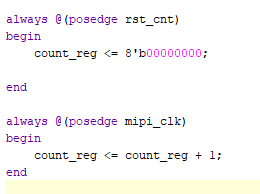

Hello, I want a status to be maintained for a certain period of time. For example, assigning the output to a certain value for 100ns. I thought of a method for this, but I don't know if it makes sense. There will be a counter module and it will count continuously until the reset signal arrives. If we send a reset signal to this counter module from the main structure, it will reset once and continue to count again. I do the reset event in the combinatorial always block, but the reset signal is connected to the main clock. What are your suggestions, is there a more logical way or is this way valid?